### REPUBLIQUE ALGERIENNE DEMOCRATIQUE ET POPULAIRE

وزارة التعليم العالي و البحث العلمي

Ministère de l'Enseignement Supérieur et de la Recherche Scientifique

جامعة الدكتور الطاهر مولاي سعيدة-

Université Saida Dr Tahar Moulay – Faculté de TECHNOLOGIE

### **MEMOIRE**

Projet de recherche présenté pour l'obtention du Diplôme de MASTER

**En** : Électronique

**Spécialité**: Instrumentation

### Sujet

### Conception et réalisation d'un véhicule omnidirectionnel avec système embarqué FPGA pour des applications d'intelligence artificielle

Présenté par : MAHMOUDI Sara Chafika

Soutenue publiquement, Juin 2025, devant le jury composé de :

Mr. CHAMI NadirMCBUniv. SaidaPrésidentMelle. SEGHIER SalimaMCBUniv. SaidaEncadrantMelle. MOSTEFAI LotfiMCAUniv. SaidaExaminateur

### **RESUME:**

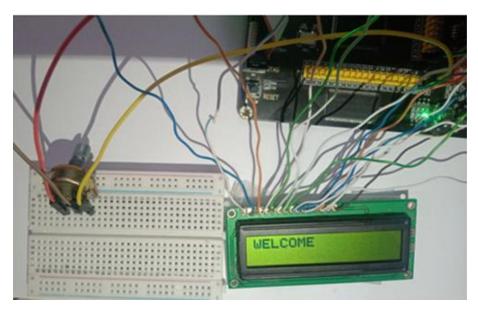

Les FPGAs (Field Programmable Gate Arrays) sont des circuits électroniques parallèles qui permettent aujourd'hui de développer des applications de plus en plus performantes en vitesse d'exécution et gourmandes en ressources matérielles. Notre projet, s'inscrit dans le cadre de la conception de systèmes embarqués intelligents, en exploitant la puissance des FPGA pour la commande en temps réel d'un véhicule mobile omnidirectionnel. L'objectif principal est de réaliser un robot capable de se déplacer dans toutes les directions, d'interagir avec son environnement, et de fonctionner à la fois en mode manuel (piloté par Bluetooth via une application mobile) et en mode autonome (avec prise de décision basée sur un capteur à ultrasons). Dans une première phase, le véhicule est commandé manuellement à l'aide d'une application mobile développée avec MIT App Inventor, qui envoie des instructions via un module Bluetooth HC-05. Le FPGA, programmé en VHDL, interprète ces commandes pour contrôler les moteurs et assurer des déplacements fluides dans toutes les directions. Un écran LCD est intégré au système pour fournir une interface visuelle, permettant par exemple l'affichage d'un message d'accueil (« WELCOME ») ou des distances mesurées par un capteur ultrasonique HC-SR04. Dans une deuxième phase, le véhicule fonctionne en mode autonome. Il détecte les obstacles dans son environnement à l'aide du capteur ultrasonique. Si un objet est détecté à moins de 30 cm, le buzzer s'active automatiquement, et le véhicule change de trajectoire en effectuant une rotation vers la gauche, illustrant une logique décisionnelle simple, caractéristique d'une IA embarquée de premier niveau. Une extension importante du projet concerne la sécurisation de l'accès au véhicule par identification sans contact, grâce à l'intégration d'un module RFID PN532. Lorsqu'un badge RFID autorisé est présenté, le FPGA valide l'identifiant reçu via une communication UART, et actionne un servomoteur pour ouvrir automatiquement la porte du véhicule, indiquant un refus d'accès. Ce système illustre une application pratique de la reconnaissance RFID dans un contexte embarqué sécurisé, avec un contrôle précis du mouvement via PWM. Ce projet met ainsi en œuvre de manière concrète l'intégration de différents modules : capteurs, moteurs, interface utilisateur, logique VHDL, communication sans fil, authentification RFID, et prise de décision autonome. Il démontre la pertinence des FPGA dans la robotique mobile intelligente et ouvre des perspectives vers des systèmes plus avancés, combinant mobilité, sécurité et intelligence embarquée.

### **MOTS CLES:**

FPGA, VHDL, Cyclone IV, Systèmes embarqués, Robot mobile omnidirectionnel, Mode autonome, Bluetooth, RFID, UART, MIT App Inventor, logiciel Qartus II.

### **Abstract:**

FPGAs (Field Programmable Gate Arrays) are parallel electronic circuits that today make it possible to develop applications with increasingly high execution speeds and demanding hardware resources. Our project is part of the design of intelligent embedded systems, exploiting the power of FPGAs for real-time control of an omnidirectional mobile vehicle. The main objective is to create a robot capable of moving in all directions, interacting with its environment, and operating both in manual mode (controlled by Bluetooth via a mobile application) and in autonomous mode (with decision-making based on an ultrasonic sensor). In a first phase, the vehicle is manually controlled using a mobile application developed with MIT App Inventor, which sends instructions via an HC-05 Bluetooth module. The FPGA, programmed in VHDL, interprets these commands to control the motors and ensure smooth movements in all directions. An LCD screen is integrated into the system to provide a visual interface, allowing for example the display of a welcome message ("WELCOME") or distances measured by an HC-SR04 ultrasonic sensor. In a second phase, the vehicle operates in autonomous mode. It detects obstacles in its environment using the ultrasonic sensor. If an object is detected within 30 cm, the buzzer is automatically activated, and the vehicle changes trajectory by rotating to the left, illustrating a simple decision logic, characteristic of a first-level embedded AI. An important extension of the project concerns securing vehicle access by contactless identification, thanks to the integration of a PN532 RFID module. When an authorized RFID badge is presented, the FPGA validates the received identifier via UART communication, and activates a servomotor to automatically open the vehicle door, indicating a refusal of access. This system illustrates a practical application of RFID recognition in a secure embedded context, with precise movement control via

PWM. This project thus concretely implements the integration of different modules: sensors, motors, user interface, VHDL logic, wireless communication, RFID authentication, and autonomous decision-making. It demonstrates the relevance of FPGAs in intelligent mobile robotics and opens up perspectives towards more advanced systems, combining mobility, security and embedded intelligence.

### **Keywords:**

FPGA, VHDL, Cyclone IV, Embedded Systems, Omnidirectional Mobile Robot, Autonomous Mode, Bluetooth, RFID, UART, MIT App Inventor, Qartus II Software.

### ملخص

FPGA (مصفوفات البوابات القابلة للبرمجة) عبارة عن دوائر الكترونية متوازية تتيح اليوم إمكانية تطوير تطبيقات ذات كفاءة متزايدة في سرعة التنفيذ وتتطلب موارد الأجهزة. مشروعنا جزء من تصميم أنظمة مُدمجة ذكية، تُستغل قوة مصفوفات البوابات القابلة للبرمجة ميدانيًا للتحكم الفوري في مركبة متنقلة متعددة الاتجاهات. الهدف الرئيسي هو إنشاء روبوت قادر على الحركة في جميع الاتجاهات، والتفاعل مع بيئته، والعمل في الوضع اليدوي (يتم التحكم فيه عبر البلوتوث عبر تطبيق جوال) والوضع الذاتي (مع اتخاذ قرارات بناءً على مستشّعر فوق صوتى). في المرحلة الأولى، يتم التحكم في المركبة يدويًا باستخدام تطبيق جوال مُطور بالتعاون مع MIT App Inventor، والذي يُرسُلُ التّعليمات عبر وحدة بلوتوتُ HC-05. تُفسر مصفوفةُ البوابات القابلة للبرمجة ميدانيًّا (FPGAs)، أَلْمُبرمجة بلغة VHDL، هذه الأوامر للتحكم في المحركات وضمان حركة سلسة في جميع الاتجاهات. شاشة LCD مُدمجة في النظام لتوفير واجهة مرئية، تسمح، على سبيل المثال، بعرض رسالة ترحيب ("WELCOME") أو المسافات التي يُقاسها مستشعر ُ فوق صُوتي HC-SR04. في المرحلة الثانية، تعمل المركبة في وضع التشغيل الذاتي. تكتشف العوائق في بيئتها باستخدام مستشعر الموجات فوق الصوتية. في حاٍل اكتشاف جسم ضمن نطاق 30 سم، يُفعَل الجرس تلقَائيًا، وتغيّر المركبة مُسارها بالالتفاف إلى اليسار، مما يُظهر منطق قرار بسيطًا، وهو سمة من سمات الذكاء الاصطناعي المدمج من المستوى الأول. ومن الإضافات المهمة للمشروع تأمين دخول المركبة عبر تحديد الهوية بدون تلامس، وذلك بفضل دمج وحدة PN532 RFID. عند تقديم شارة RFID معتمدة، يتحقق FPGA من صحة المعرف المُستلم عبر اتصال UART، ويُفعَل محرك سيرفو لفتح باب المركبة تلقائيًا، مُشيرًا إلى رفض الدخول. يُوضح هذا النظام تطبيقًا عمليًا للتعرف على RFID في سياق مدمج آمن، مع تحكم دقيق في الحركة عبر PWM. وبالتالي، يُطبّق هذا المشروع بشكل ملموس دمج وحدات مختلفة: المستشعرات، والمحركات، وواجّهة المستخدم، ومنطق VHDL، والاتصالات اللاسلكية، ومصادقة RFID، واتخاذ القرارات بشكل ذاتي. ويوضح أهمية FPGAs في مجال الروبوتات المتنقلة الذكية ويفتح آفاقًا نحو أنظمة أكثر تقدمًا، تجمع بين التنقل والأمان والذكاء المضمن.

### الكلمات الدالة:

Cyclone IV ، VHDL ، FPGA ، الأنظمة المضمنة، الروبوت المتنقل متعدد الاتجاهات، الوضع المستقل، البلوتوث، RFID، Qartus IV ، VHDL ، FPGA . برنامج Qartus II ، برنامج

### **SOMMAIRE**

| Remerciement                                                                   |

|--------------------------------------------------------------------------------|

| Dédicace Résumé                                                                |

| Sommaire                                                                       |

| Liste des Figures                                                              |

| Liste des Tableaux                                                             |

| Liste D'abréviation                                                            |

| Introduction Générale1                                                         |

| ChapitreI:Circuits logiques programmables FPGA                                 |

| I.1 Introduction5                                                              |

| <b>I.2 Circuits Logiques Programmables du type</b> FPGA5                       |

| I.2.1 Définition du FPGA5                                                      |

| I.2.2 Architecture                                                             |

| I.2.3 FPGAs : illustration avec la famille Cyclone IV d'Altera11               |

| I.2.3.1 Puissance de circuit Cyclone IV                                        |

| I.2 .3.2 Programmation d'un périphérique de configuration série                |

| I.2 .3.3 Caractéristiques de Cyclone IV EP4CE10 FPGA19                         |

| I.3 Principaux fondeurs d'FPGA                                                 |

| I.4 Configuration et reconfiguration des FPGA20                                |

| I.5 Avantages du FPGA                                                          |

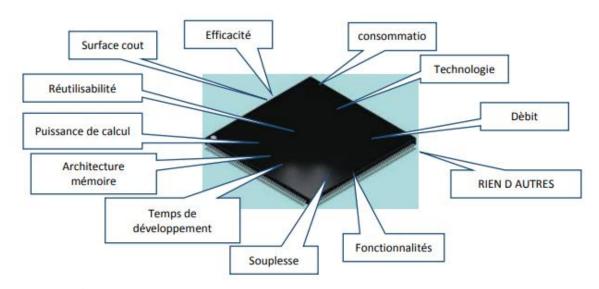

| I.6 Critères de choix du circuit programmable FPGA21                           |

| I.7 Méthodologie de conception                                                 |

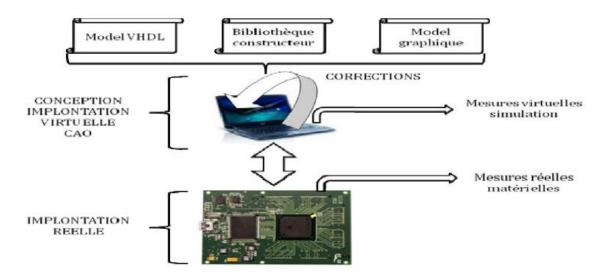

| I.7.1 Outils de CAO (Conception Assistée par Ordinateur) pour la configuration |

| d'un FPGA22                                                                    |

| I.7.1 Outils de CAO (Conception Assistée par Ordinateur) pour la configuration |

| d'un FPGA22                                                                    |

| I.7.1.1 Spécification du design                                                |

| I.7.1.2 Développement du design                                                |

| I.7.1.3 Synthèse                                                                                                                                                                                                                                                                                                               | 23                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| I.7.1.4 Placement et routage                                                                                                                                                                                                                                                                                                   | 24                   |

| I.7.1.5 Intégration et implémentation                                                                                                                                                                                                                                                                                          | 24                   |

| I.8 Principales applications des FPGA                                                                                                                                                                                                                                                                                          | 25                   |

| I.8.1 Les applications spécifiques d'un FPGA comprennent.                                                                                                                                                                                                                                                                      | 25                   |

| I.8.2 L'application d'un FPGA dans le do                                                                                                                                                                                                                                                                                       | maine d'intelligence |

| artificielle                                                                                                                                                                                                                                                                                                                   | 26                   |

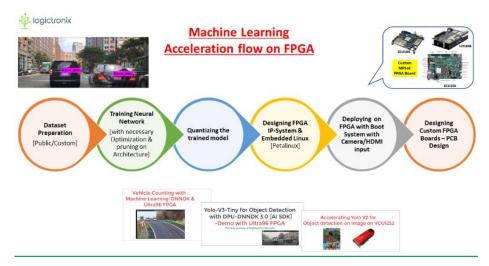

| I.8.2.1 Accélération de l'IA avec les FPGA                                                                                                                                                                                                                                                                                     | 26                   |

| I.8.2.2 Projets de machine learning sur FPGA                                                                                                                                                                                                                                                                                   | 26                   |

| I.8.2.3 Systèmes avancés d'aide à la conduite                                                                                                                                                                                                                                                                                  | 27                   |

| I.8.2.4 Fusion de capteurs et prise de décision                                                                                                                                                                                                                                                                                | 28                   |

| I.8.2.5 Contrôle des moteurs et gestion de l'énergie                                                                                                                                                                                                                                                                           | 28                   |

| I.9 Conclusion                                                                                                                                                                                                                                                                                                                 | 29                   |

| Référence bibliographiques chapitre I                                                                                                                                                                                                                                                                                          | 30                   |

|                                                                                                                                                                                                                                                                                                                                |                      |

| Chapitre II : Présentation de langage VHDL                                                                                                                                                                                                                                                                                     |                      |

| II.1 Introduction                                                                                                                                                                                                                                                                                                              | 33                   |

| II.1 Introduction                                                                                                                                                                                                                                                                                                              | 33                   |

| II.1 Introduction  II.2Langagesde description matérielle  II.2.1 Historique                                                                                                                                                                                                                                                    | 33<br>34<br>34       |

| II.1 Introduction  II.2Langagesde description matérielle  II.2.1 Historique  II.2.2 Langages HDL                                                                                                                                                                                                                               | 33<br>34<br>34<br>35 |

| II.1 Introduction.  II.2Langagesde description matérielle.  II.2.1 Historique.  II.2.2 Langages HDL.  II.2.3 Langage de description matérielle VHDL.                                                                                                                                                                           |                      |

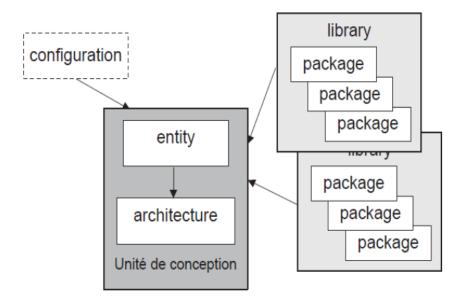

| II.1 Introduction.  II.2Langagesde description matérielle.  II.2.1 Historique.  II.2.2 Langages HDL.  II.2.3 Langage de description matérielle VHDL.  II.2.3.1 Structure d'un programme VHDL.                                                                                                                                  |                      |

| II.1 Introduction.  II.2Langagesde description matérielle.  II.2.1 Historique.  II.2.2 Langages HDL.  II.2.3 Langage de description matérielle VHDL.  II.2.3.1 Structure d'un programme VHDL.  II.2.3.1.1 Entête.                                                                                                              |                      |

| II.1 Introduction.  II.2Langagesde description matérielle.  II.2.1 Historique.  II.2.2 Langages HDL.  II.2.3 Langage de description matérielle VHDL.  II.2.3.1 Structure d'un programme VHDL.  II.2.3.1.1 Entête.  II.2.3.1.2 Déclaration des librairies.                                                                      |                      |

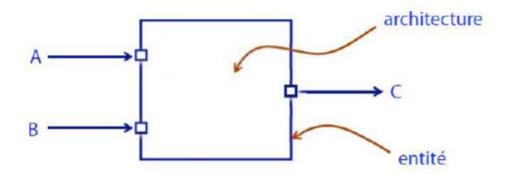

| II.1 Introduction.  II.2Langagesde description matérielle.  II.2.1 Historique.  II.2.2 Langages HDL.  II.2.3 Langage de description matérielle VHDL.  II.2.3.1 Structure d'un programme VHDL.  II.2.3.1.1 Entête.  II.2.3.1.2 Déclaration des librairies.  II.2.3.1.3 Déclaration d'entité.                                    |                      |

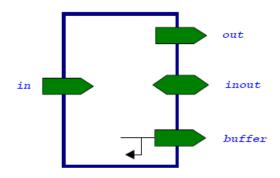

| II.1 Introduction.  II.2Langagesde description matérielle.  II.2.1 Historique.  II.2.2 Langages HDL.  II.2.3 Langage de description matérielle VHDL.  II.2.3.1 Structure d'un programme VHDL.  II.2.3.1.1 Entête.  II.2.3.1.2 Déclaration des librairies.  II.2.3.1.3 Déclaration d'entité.  II.2.3.1.3 Signal d'entré/sortie. |                      |

| II.1 Introduction.  II.2Langagesde description matérielle.  II.2.1 Historique.  II.2.2 Langages HDL.  II.2.3 Langage de description matérielle VHDL.  II.2.3.1 Structure d'un programme VHDL.  II.2.3.1.1 Entête.  II.2.3.1.2 Déclaration des librairies.  II.2.3.1.3 Déclaration d'entité.                                    |                      |

| II.2.3.1.4.3 Description mixte                                     | 43 |

|--------------------------------------------------------------------|----|

| II.2.3.2 Relation entre une structure VHDL et un circuit numérique | 44 |

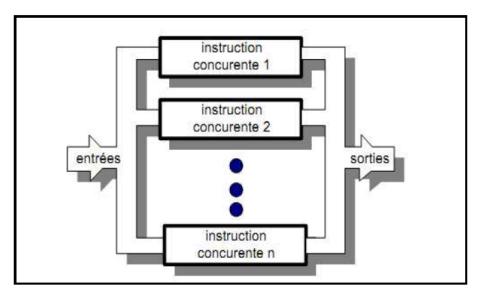

| II.2.4 Types d'instructions utilisées en VHDL                      | 45 |

| II.2.4.1 Instructions concurrentes                                 | 45 |

| II.2.4.1.1 Affectation simple                                      | 45 |

| II.2.4.1.2 Affectation conditionnelle                              | 45 |

| II.2.4.1.3 Affectation sélective                                   | 46 |

| II.2.4.1.4 Instanciation du composant                              | 46 |

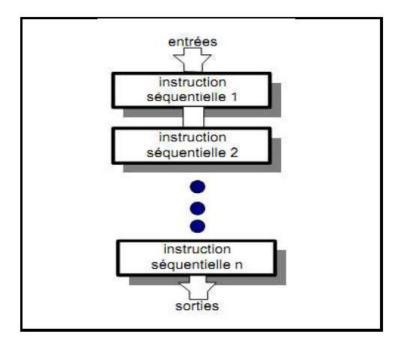

| II.2.4.2 Instructions séquentielles                                | 46 |

| II.2.4.2.1 Définition d'un process.                                | 46 |

| II.2.4.2.2 Principales instructions utilisées dans un process      | 47 |

| II.2.4.2.2.1 Instruction conditionnelle                            | 47 |

| II.2.4.2.2.2 Instruction de choix                                  | 48 |

| II.2.4.2.2.3 Instruction wait                                      | 48 |

| II.2.4.2.2.4 Boucles                                               | 48 |

| II.2.5 Opérateurs de base                                          | 49 |

| II.2.5.1 Opérations logiques                                       | 49 |

| II.2.5.2 Opérations relationnelles                                 | 50 |

| II.2.5.3 Opérations d'addition                                     | 50 |

| II.2.5.4 Opérations de signe                                       | 50 |

| II.2.5.5 Opérations de multiplication                              | 50 |

| II.2.5.6 Opérations NOT, ABS et **                                 | 51 |

| II.2.5.7 Sous programmes                                           | 51 |

| II.2.5.7.1 Fonctions                                               | 51 |

| II.2.5.7.2 Procédures.                                             | 52 |

| II.3 Différences entre VHDL et un langage de programmation         | 53 |

| II.4 Vérification d'une conception VHDL                            | 53 |

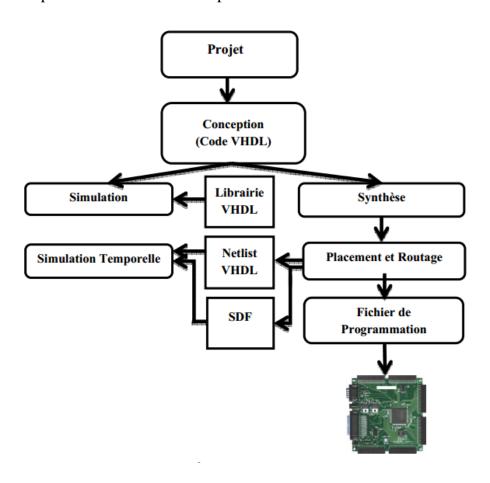

| II.5 Développement d'un projet en VHDL                             | 54 |

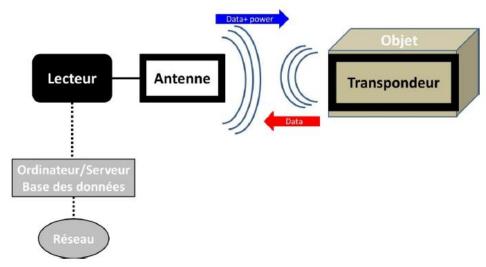

| II.6Technologie RFID.                                              | 55 |

| II.6.1 Définition générale d'un système RFID                       | 56 |

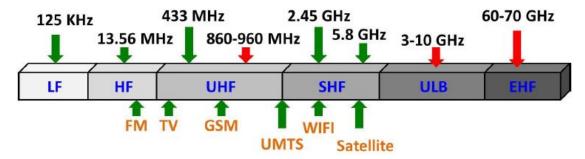

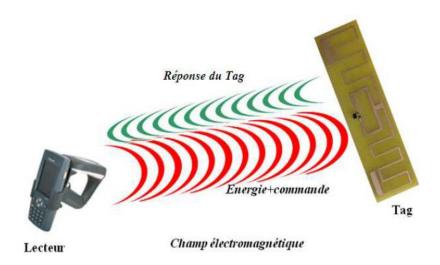

| II.6.2 Principe de fonctionnement d'un système RFID             | 58              |

|-----------------------------------------------------------------|-----------------|

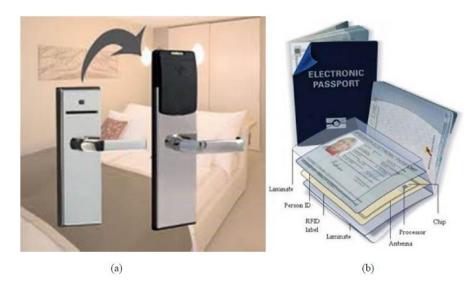

| II.6.3Domaines d'application de la technologie RFID             | 59              |

| II.7 Conclusion                                                 | 60              |

| Référence bibliographiques chapitre II                          | 61              |

|                                                                 |                 |

| Chapitre III Résultats de conception et réalisation d'un véhicu | le utilisant un |

| FPGA                                                            |                 |

|                                                                 |                 |

| III.1 Introduction                                              | 63              |

| III.2 Partie Hardware : présentation des outils électroniques   | 64              |

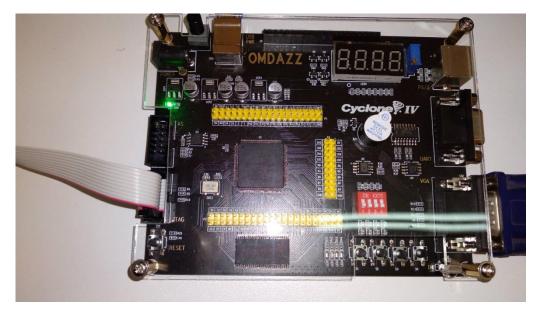

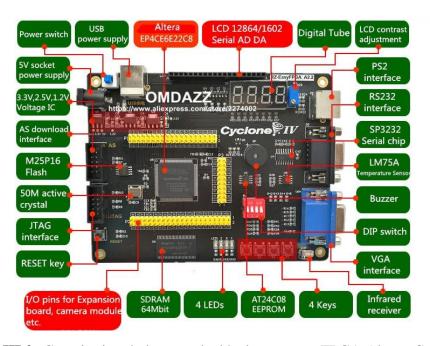

| III.2.1 Carte de développement d'Altera                         | 64              |

| III.2.1.1 Caractéristiques de notre composant FPGA EP4CE10E22   | 2C865           |

| III.2.1.2 Différentes parties de la carte OMDAZZ                | 65              |

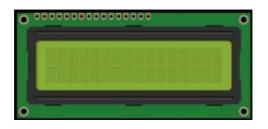

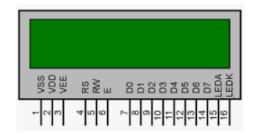

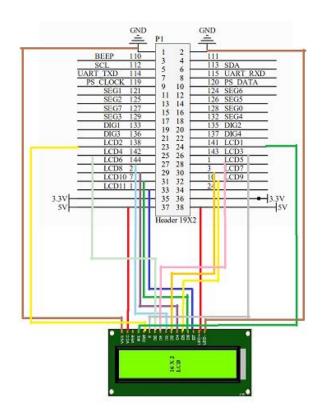

| III.2.2 Module de LCD 16x2                                      | 67              |

| III.2.2.1 Caractéristiques                                      | 67              |

| III.2.2.2 Brochage (interface 16 broches)                       | 67              |

| III.2.2.3 Fonctionnement                                        | 68              |

| III.2.2.4 Câblage d'afficheur LCD 16x2                          | 68              |

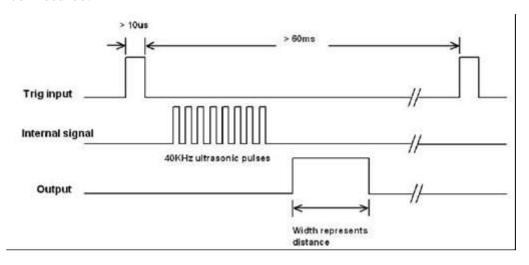

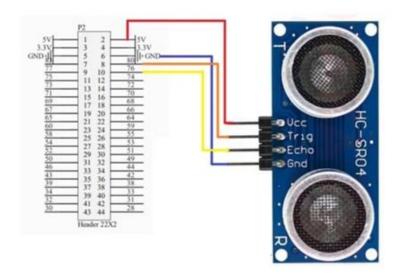

| III.2.3 Module de détecteur HC-SR04                             | 69              |

| III.2.3.1 Caractéristiques                                      | 69              |

| III.2.3.2 Broches de connexion                                  | 69              |

| III.2.3.3 Fonctionnement                                        | 70              |

| III.2.3.4 Spécifications et limites                             | 70              |

| III.2.3.5 Câblage de détecteur a ultrason avec FPGA             | 70              |

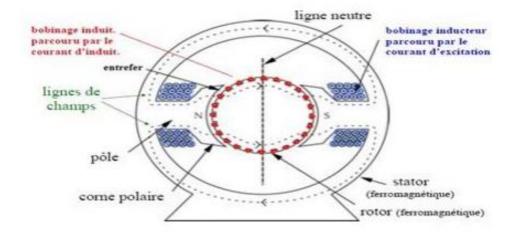

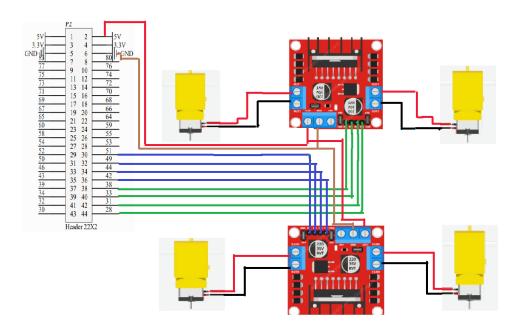

| III.2.4 Moteurs DC                                              | 71              |

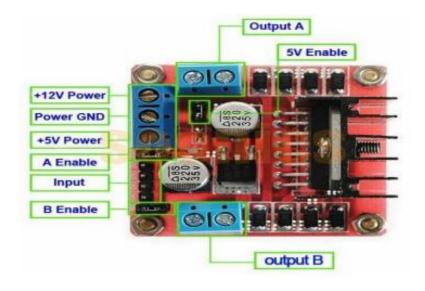

| III.2.5 Driver L298N                                            | 72              |

| III.2.5.1 Caractéristiques                                      | 72              |

| III.2.5.2 Câblage de FPGA, moteurs DC et L298N                  | 73              |

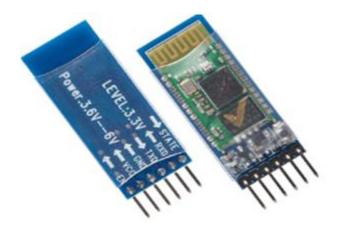

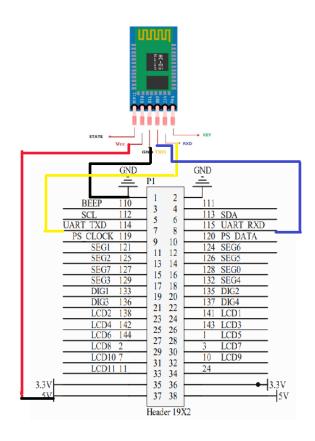

| III.2.6 Module Bluetooth HC 05                                  | 73              |

| III.2.6.1 Câblage de FPGA avec module Bluetooth HC 05           | 74              |

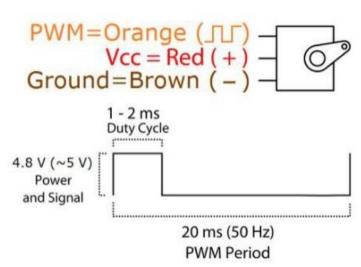

| III.2.7 Module servomoteur                                      | 74              |

|      | III.2.7.1 Caractéristiques de SG90.                                      | 75    |

|------|--------------------------------------------------------------------------|-------|

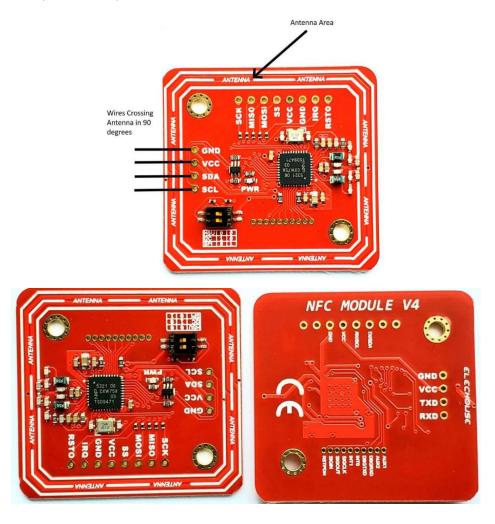

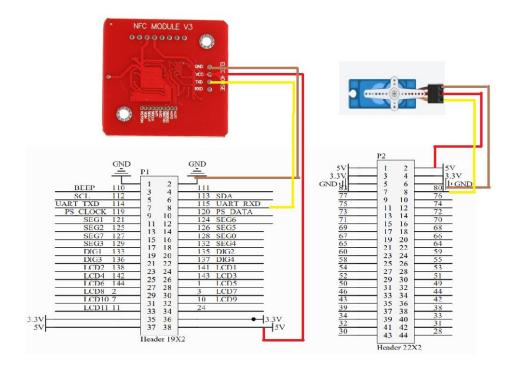

|      | III.2.8 Module RFID PN532.                                               | 76    |

|      | III.2.8.1 Caractéristiques principales                                   | 76    |

|      | III.2.8.2 Modes de fonctionnement                                        | 77    |

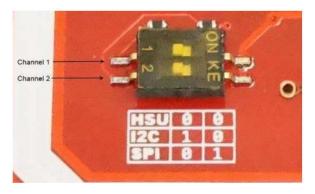

|      | III.2.8.3 Interfaces de communication.                                   | 77    |

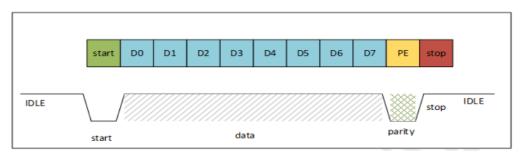

|      | III.2.8.4 UART (Universal Asynchronous Receiver and Transmitter)         | 78    |

|      | III.2.8.5 Câblage de FPGA, le servomoteur et le RFID PN532               | 79    |

|      | III.2.9Roue omnidirectionnelle                                           | 79    |

| III. | .3 Partie software                                                       | 80    |

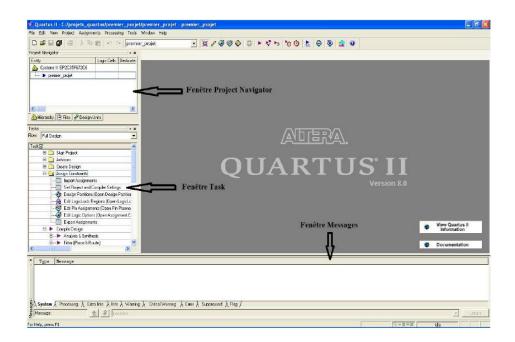

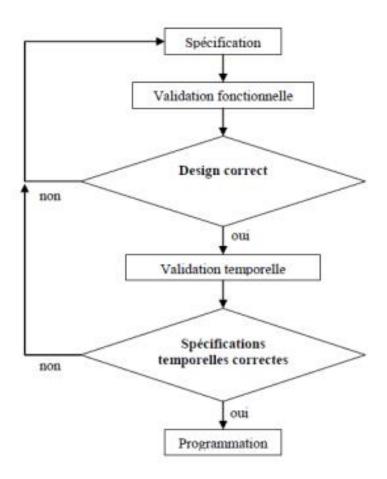

|      | III.3.1 Plateforme de développement Quartus II                           | 80    |

|      | III.3.2 Déroulement de la conception                                     | 81    |

| III. | 4 Utilisation d'un FPGA/VHDL pour afficheur LCD 16x2 : affichage         | d'un  |

| me   | ssage « WELCOME »                                                        | 82    |

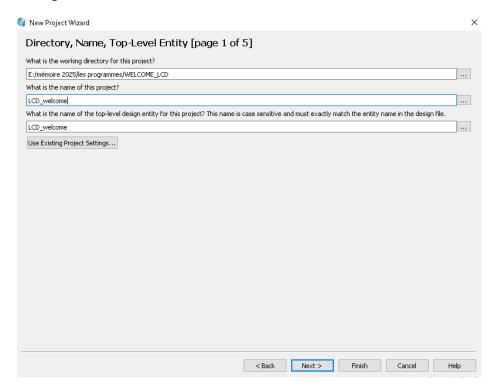

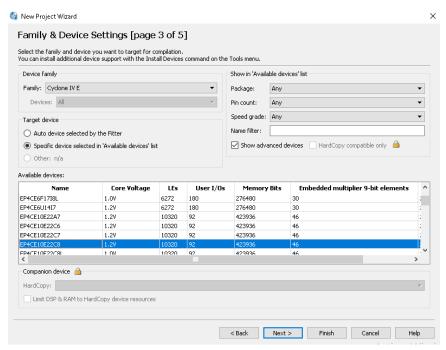

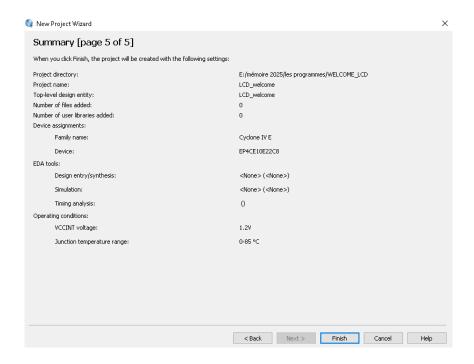

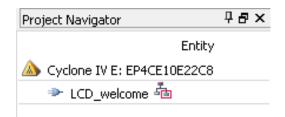

|      | III.4.1 Création d'un projet                                             | 82    |

|      | III.4.2 Ajout des sources VHDL                                           | 85    |

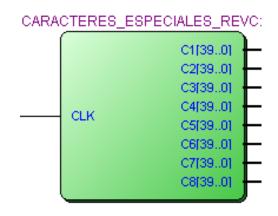

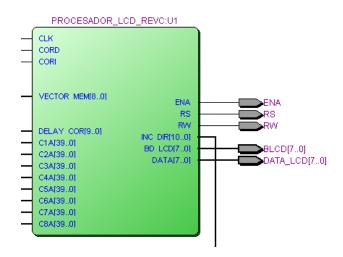

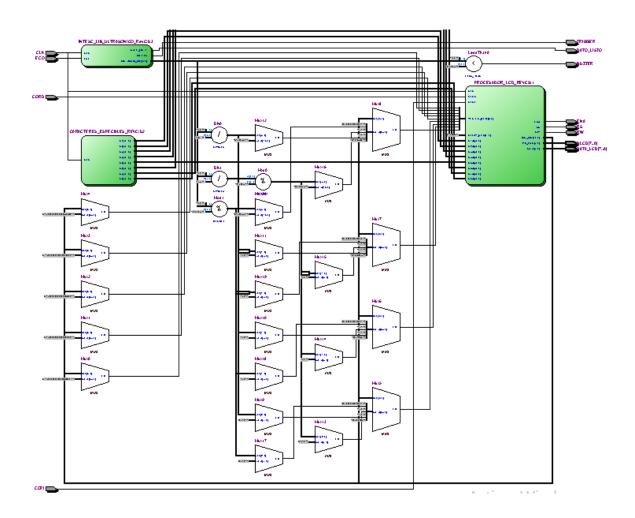

|      | III.4.2.1 Module CARACTERES_ESPECIALES_REVC                              | 85    |

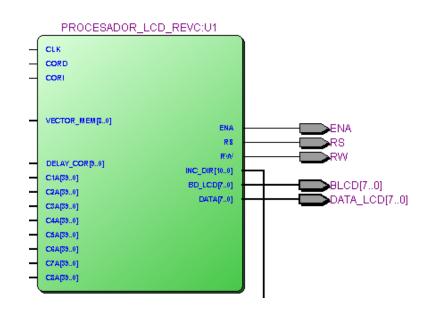

|      | III.4.2.2 Module PROCESADOR_LCD_REVC                                     | 86    |

|      | III.4.2.3 Package COMANDOS_LCD_REVC                                      | 86    |

|      | III.4.2.4 Code principale (LCD_welcome)                                  | 86    |

|      | III.4.3 Sauvegarde d'un projet                                           | 87    |

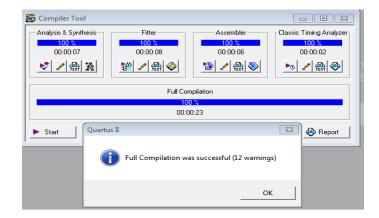

|      | III.4.4 Compilation.                                                     | 87    |

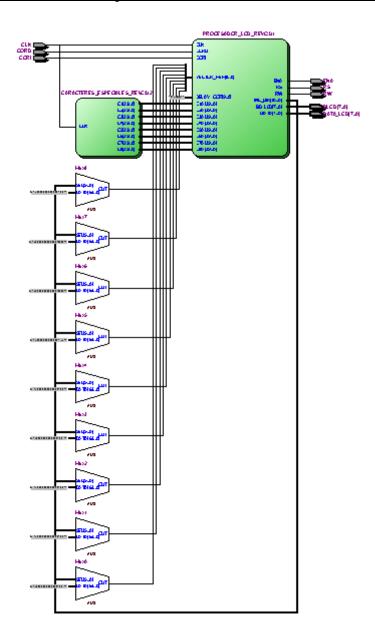

|      | III.4.5 Schéma fonctionnel (RTL : Register Transfer Level)               | 87    |

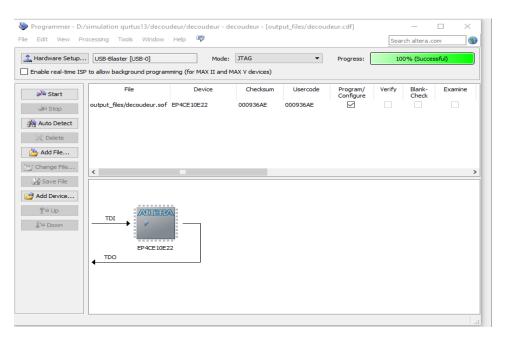

|      | III.4.6 Programmation de la maquette Cyclone IV                          | 88    |

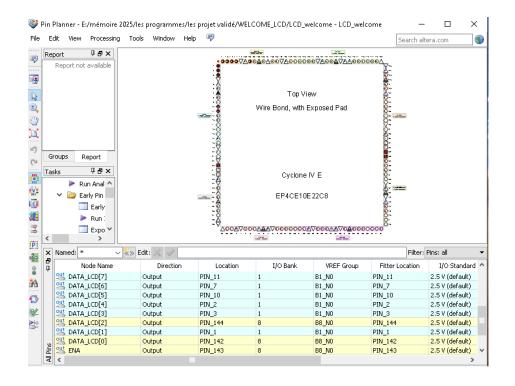

|      | III.4.6.1 Affectation des pins                                           | 88    |

|      | III.4.6.2 Programmation du circuit                                       | 90    |

| III. | .5 Utilisation d'un FPGA/VHDL pour la détection des obstacles et la mesu | re de |

| la   | distance en utilisant un capteur ultrasonique et afficheur               | LCD   |

| 16x  | x2                                                                       | 92    |

| ш    | 5.1 Codes VHDI                                                           | 02    |

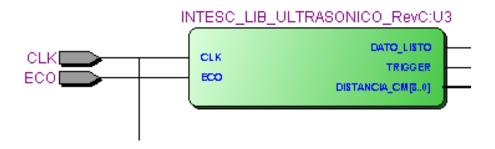

| III.5.1.1CapteurUltrasonique (INTESC_LIB_ULTRASONICO_RevC)92         | 2  |

|----------------------------------------------------------------------|----|

| III.5.1.2 Module PROCESADOR_LCD_REVC93                               | 3  |

| III.5.1.3 Module CARACTERES_ESPECIALES_REVC93                        | }  |

| III.5.1.4 Module DIVISION_ULTRASONICO_RevA94                         | 1  |

| III.5.1.5 Module COMANDOS_LCD_REVC94                                 | 4  |

| III.5.1.6 Module principal LIB_LCD_INTESC_REVC94                     | 1  |

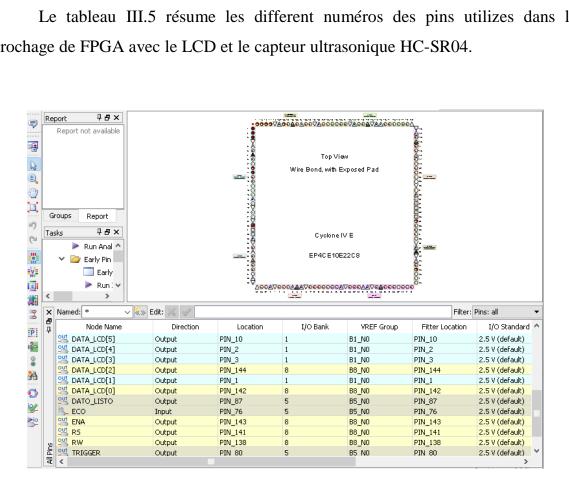

| III.5.2 Affectation des pins90                                       | 6  |

| III.5.3 Résultats d'affichage des différentes distances              | 7  |

| III.6 Utilisation d'un FPGA/VHDL pour réaliser un véhicul            | le |

| omnidirectionnel97                                                   | 7  |

| III.6.1 Sources VHDL98                                               | 3  |

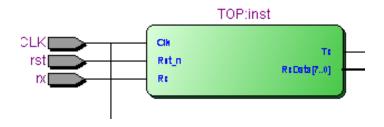

| III.6.1.1 Module UART_rs232_tx9                                      | 7  |

| III.6.1.1.1 Fonctionnement du module VHDL UART_rs232_tx9             | 7  |

| III.6.1.2 Module UART_rs232_rx10                                     | 0  |

| III.6.1.2.1 Fonctionnement du module VHDL UART_rs232_tx10            | 0  |

| III.6.1.3 UART_BaudRate_generator                                    | 1  |

| III.6.1.4 TOP                                                        | 1  |

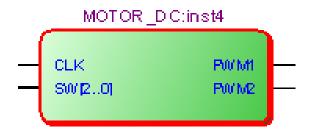

| III.6.1.5 MOTOR_DC102                                                | 2  |

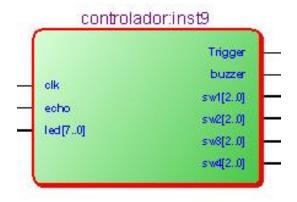

| III.6.1.6 Controlador                                                | 2  |

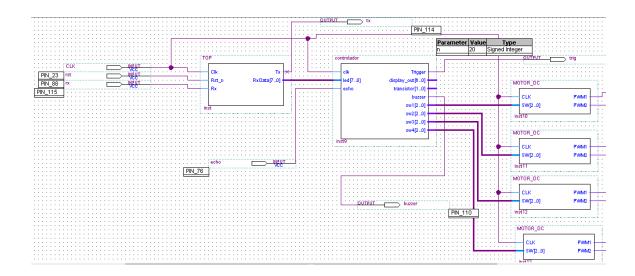

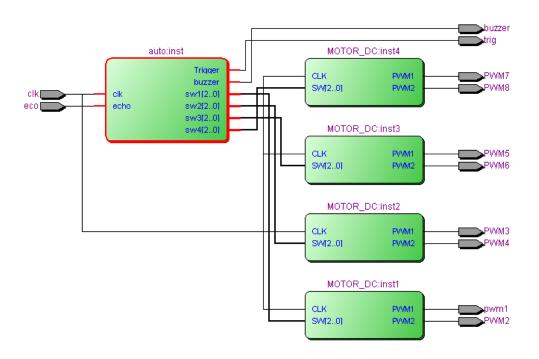

| III.6.2 Schéma bloc de projet10                                      | 3  |

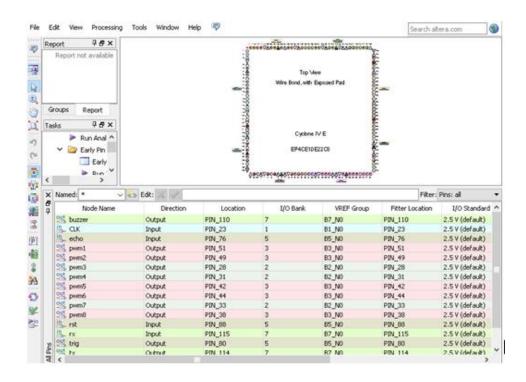

| III.6.3 Affectation des pins                                         | 3  |

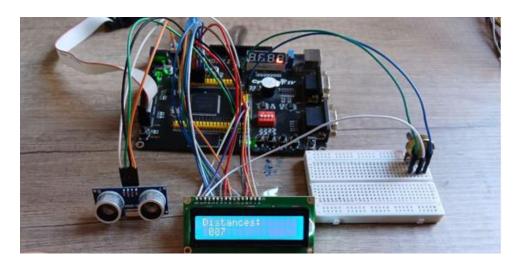

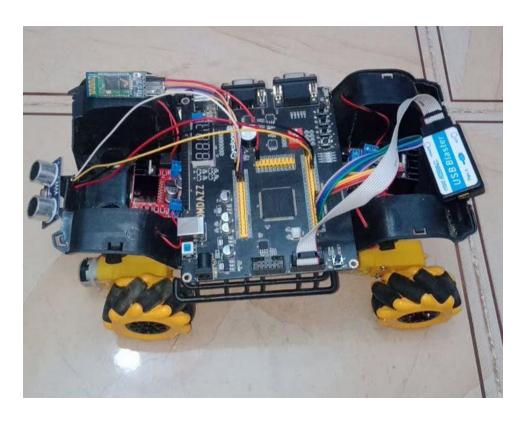

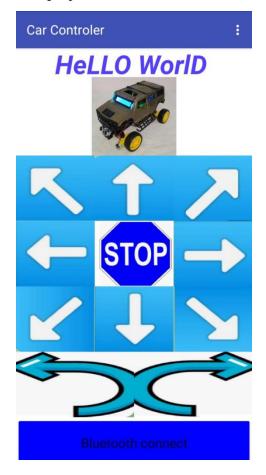

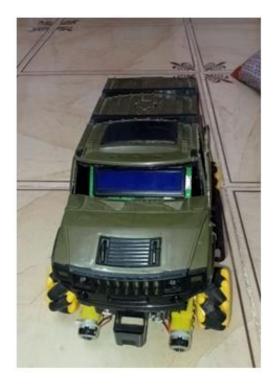

| III.6.4 Résultats de notre véhicule omnidirectionnel                 | 5  |

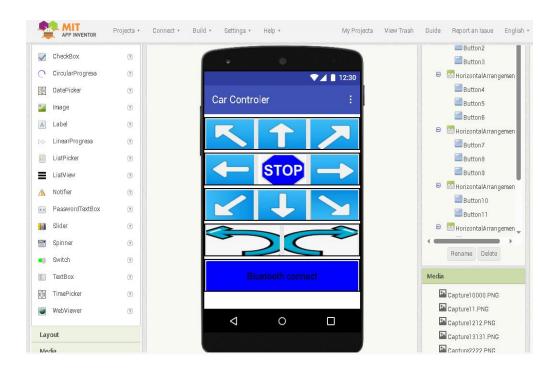

| III.6.5 Application MIT App Inventor pour le contrôle du Véhicule vi | ia |

| Bluetooth10                                                          | 6  |

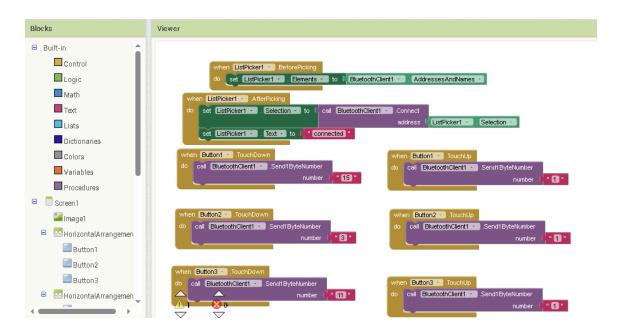

| III.6.5.1 Etapes de la création de l'application                     | ;  |

| III.7 Utilisation d'un FPGA/VHDL pour la réalisation du véhicule     |    |

| autonome11                                                           | 0  |

| III.7.1 Sources VHDL                                                 |    |

| III.7.1.1 MOTOR_DC110                                                |    |

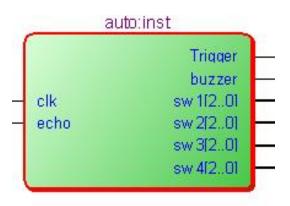

| III.7.1.2 Auto                                                       |    |

| III.7.1.3 <b>S</b> chéma fonctionnel RTL du code principal d | u véhicule       |

|--------------------------------------------------------------|------------------|

| autonom                                                      | 112              |

| III.7.2 Affectation des pins                                 | 112              |

| III.7.3 Résultat de conception et réalisation de autonome    |                  |

| III.8 Utilisation d'un FPGA/VHDL pour l'ouverture de la      | ı porte de notre |

| véhicule en utilisant la technologie RFID                    | 114              |

| III.8.1 Sources VHDL                                         | 114              |

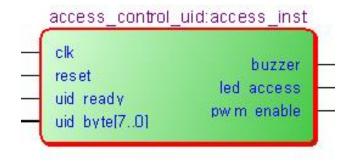

| III.8.1.1 access_control_uid                                 | 114              |

| III.8.1.2 pn532_parser                                       | 115              |

| III.8.1.3 pwm_generator                                      | 115              |

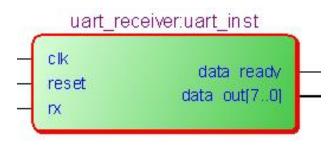

| III.8.1.4 uart_receiver                                      | 116              |

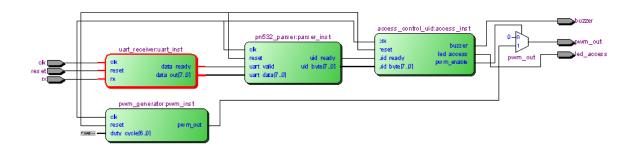

| III.8.1.5 top_level (code principale)                        | 116              |

| III.8.2 Affectation des pins                                 | 117              |

| III.8.3 Résultat d'ouverture de la porte                     | 118              |

| III.9 Conclusion                                             | 120              |

| Référence bibliographiques chapitre III                      | 122              |

| Conclusion générale                                          | 123              |

### LISTE DES FIGURES

| FigureI.1: Image d'un circuit FPGA6                                                        |

|--------------------------------------------------------------------------------------------|

| Figure I.2: Architecture interne des FPGAs                                                 |

| Figure I.3: Different secateurs d'un FPGA8                                                 |

| <b>Figure I.4:</b> Exemple de blocs logiques de different fabricants9                      |

| Figure I.5: Structure générale du routage10                                                |

| Figure I.6: Symbol de Cyclone IV d'Altera11                                                |

| Figure I.7: Caractéristiques architecturales clés du FPGA Cyclone IV12                     |

| Figure I.8: Structure d'un LogicElement LE                                                 |

| Figure I.9: Connexions chaînées entre LEs dans un LAB de circuit Cyclone                   |

| IV15                                                                                       |

| Figure I.10: Structure LAB de circuit Cyclone IV                                           |

| Figure I.11: Puissance Cyclone IV E (à gauche) et Cyclone IV GX (à droite)18               |

| Figure I.12: Programmation d'un périphérique de configuration série avec une               |

| solution de chargeur flash série19                                                         |

| Figure I.13: Statistiques du marché occupé par les vendeurs d'FPGA19                       |

| <b>Figure I.14:</b> Reprogrammabilité sur site d'un FPGA20                                 |

| Figure I.15: Critères de choix du circuit logique programmable FPGA22                      |

| Figure I.16: Mode d'exécution matériel des outils de CAO                                   |

| Figure I.17: Cycle de programmation d'un FPGA en utilisant les outils de                   |

| CAO25                                                                                      |

| Figure I.18 : Illustration représentative de l'accélération de l'intelligence artificielle |

| (IA) à l'aide des FPGA26                                                                   |

| Figure I.19: Illustrations représentant des projets de machine learning sur                |

| FPGA27                                                                                     |

| Figure I.20 : Systèmes avancés d'aide à la conduite27                                      |

| Figure I.21 : Schéma de circuit FPGA pour la gestion de l'énergie28                        |

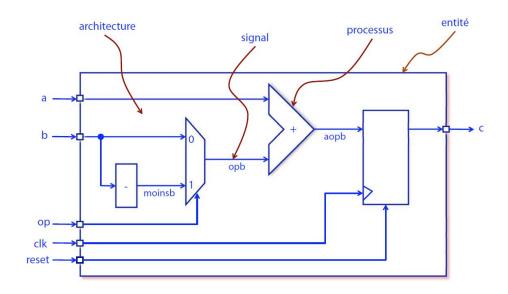

| Figure II.1: Structure de base d'un module VHDL                                            |

| <b>Figure II.2:</b> Représentation de sens de signal39                                     |

| <b>Figure II.3:</b> Représentation de l'entité et l'architecture40                         |

| Figure II.4: Relation entre les composants d'un VHDL et un circuit numér    | ique44  |

|-----------------------------------------------------------------------------|---------|

| Figure II.5: Instructions en mode concurrent                                | 45      |

| Figure II.6: Instructions en mode séquentiel                                | 47      |

| Figure II.7: Différentes étapes de l'implémentation sur FPGA                | 55      |

| Figure II.8: Eléments d'un système RFID                                     | 56      |

| Figure II.9: (a) lecteur RFID pour le contrôle d'accès, (b) passeport biomé | trique  |

| utilisant la RFID                                                           | 57      |

| Figure II.10: Bandes de fréquence                                           |         |

| RFID58                                                                      |         |

| Figure II.11: Fonctionnement général d'un système RFID                      | 59      |

| Figure III.1: Carte de développement FPGA Altera Cyclone IV                 |         |

| EP4CE10E22C8                                                                | 65      |

| Figure III.2: Constitution de la carte de développement FPGA Altera         | Cyclone |

| IV                                                                          | 66      |

| Figure III.3: Afficheur LCD 16x2                                            | 67      |

| Figure III.4: Câblage d'afficheur LCD avec le FPGA                          | 68      |

| Figure III.5: Capteur ultrason HC-SR04                                      | 69      |

| Figure III.6: Diagramme de fonctionnement du capteur ultrason               | 70      |

| Figure III.7 : Câblage de HC-SR 04 avec FPGA                                | 71      |

| Figure III.8 : Structure générale d'un moteur DC                            | 72      |

| Figure: III.9: Brochage du Module L298N double ponts en H                   | 72      |

| <b>Figure III.10 :</b> Câblage entre FPGA, les moteurs DC et driver L298N   | 73      |

| Figure III.11: Module Bluetooth HC05                                        | 74      |

| Figure III.12: Connexion entre FPGA et le module Bluetooth HC-05            | 74      |

| Figure III.13: Servomoteur SG90                                             | 75      |

| Figure III.14 : Schéma de Connexion et Caractéristiques du Signal PWM J     | our le  |

| Pilotage d'un Servomoteur                                                   | 76      |

| Figure III 15 · RFID PN532                                                  | 77      |

| Figure III.16: Cas des commutateurs pour les modes UART (HSU), I2C et         |     |

|-------------------------------------------------------------------------------|-----|

| SPI                                                                           | 8'  |

| Figure III.17: Format d'une trame de communication série UART7                | 78  |

| Figure III.18: Connexion entre FPGA, le servomoteur et le RFID PN5327         | 19  |

| Figure III.19: Roue omnidirectionnelle                                        | 19  |

| Figure III.20: Environnement de développement Quartus                         | 80  |

| Figure III.21: Déroulement de la conception.                                  | 81  |

| Figure III.22: Création d'un projet sous quartus II                           | 83  |

| Figure III.23: Fenêtre de choix du circuit                                    | 84  |

| Figure III.24: Fenêtre de création du projet finie                            | 84  |

| Figure III.25: Fenêtre de type de projet                                      | 85  |

| Figure III.26: RTL du programme VHDL                                          |     |

| « CARACTERES_ESPECIALES_REVC »                                                | 85  |

| Figure III.27: RTL du programme                                               |     |

| VHDL « PROCESADOR_LCD_REVC »                                                  | 86  |

| Figure III.28 : Fenêtre de compilation projet «LCD_welcome»                   | 87  |

| Figure III.29 : Schéma fonctionnel RTL de LCD_welcome                         | 89  |

| Figure III.30 :Fenêtre de type d'assignement des pins de l'affichage sur LCD8 | 38  |

| Figure III.31: Boite de dialogue de programmation                             | 90  |

| Figure III.32: Plateforme Cyclone IV programmée9                              | 91  |

| Figure III.33: Affichage du message « WELCOME » sur l'afficheur LCD 16x2      | .91 |

| Figure III.34: RTL du programme                                               |     |

| VHDL « INTESC_LIB_ULTRASONICO_RevC »                                          | .92 |

| Figure III.35: RTL du programme                                               |     |

| VHDL « PROCESADOR_LCD_REVC ».                                                 | 93  |

| Figure III.36: RTL du programme                                               |     |

| VHDL « CARACTERES ESPECIALES REVC »                                           | 94  |

| Figure III.37: Schéma fonctionnel RTL de code principal                                 |

|-----------------------------------------------------------------------------------------|

| « LIB_LCD_INTESC_REVC»96                                                                |

| Figure III.38: Fenêtre de type d'assignement des pins de mesure de la distance95        |

| Figure III.39 : Exemples de la distance mesurée: (a) 07 cm, (b) 36 cm97                 |

| Figure III.40: RTL du programme VHDL « TOP »                                            |

| Figure III.41: RTL du programme VHDL « MOTOR_DC »                                       |

| Figure III.42: RTL du programme VHDL « Controlador »                                    |

| Figure III.43 : Schéma bloc de projet pour réaliser un véhicule omnidirectionnel103     |

| Figure III.44: Fenêtre de type d'assignement des pins du véhicule                       |

| omnidirectionnelle                                                                      |

| Figure III.45: Photo de véhicule omnidirectionnelle avec système embarqué               |

| FPGA                                                                                    |

| Figure III.46 : Interface de l'application mobile de contrôle de véhicule via Bluetooth |

| sous MIT App Inventor                                                                   |

| Figure III.47: Bouton pour connecter avec Bluetooth                                     |

| rigure 111.47. Douton pour connecter avec Bractooth                                     |

| <b>Figure III.48:</b> Message de l'activation de Bluetooth                              |

| Figure III.49: Blocs de l'application                                                   |

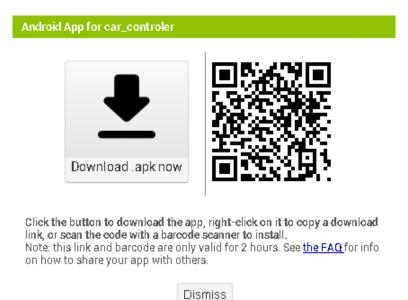

| Figure III.50 : Code QR pour le téléchargement                                          |

| Figure III.51: L'application de la manipulation de notre véhicule                       |

| Figure III.52: RTL du programme VHDL « MOTOR_DC»110                                     |

| Figure III.53: RTL du programme VHDL « auto »                                           |

| <b>Figure III.54:</b> Schéma fonctionnel RTL du véhicule autonome                       |

| <b>Figure III.55:</b> Photo du véhicule autonome avec le système embarqué FPGA113       |

| Figure III.56: RTL du programme VHDL « access_control_uid »                             |

| <b>Figure III.57 :</b> RTL du programme VHDL « pn532_parser »                           |

| Figure III.58: RTL du programme VHDL « pwm_generator »                                  |

| Figure III.59: RTL du programme VHDL « uart_receiver »                                  |

| <b>Figure III.60 :</b> RTL du programme VHDL « top_level » code principale117           |

| T | • .  | 1   | C.  |       |

|---|------|-----|-----|-------|

|   | iste | dec | †10 | IITAC |

| _ | mow  | ucs | 112 | urcs  |

| Figure III.61: Refus d'accès – Tag RFID non autorisé, porte du véhicule fermée | 119 |

|--------------------------------------------------------------------------------|-----|

| Figure III.62: Accès autorisé – Tag RFID reconnu, ouverture de la porte du     |     |

| véhicule                                                                       | 119 |

### LISTE DES TABLAUX

| Tableau II.1: Ecriture des opérateurs logique en VHDL    49                           |

|---------------------------------------------------------------------------------------|

| <b>Tableau II.2:</b> Ecriture des opérateurs relationnels en VHDL                     |

| <b>Tableau III.1:</b> Caractéristiques de FPGA EP4CE10E22C8                           |

| <b>Tableau III.2:</b> Spécifications et limites du capteur ultrason70                 |

| Tableau III.3: Etats des commutateurs pour chaque mode                                |

| Tableau III.4: Numéros des pins entrées/sorties utilisés de l'affichage sur           |

| LCD89                                                                                 |

| Tableau III.5: Numéros des pins entrées/sorties utilisés pour la mesure de la         |

| distance96                                                                            |

| Tableau III.6: Numéros des pins entrées/sorties utilisés pour notre véhicule          |

| omnidirectionnel                                                                      |

| Tableau III.7: Numéros des pins entrées/sorties utilisés pour le véhicule             |

| autonome                                                                              |

| Tableau III.8: Numéros des pins entrées/sorties utilisés pour l'ouverture d'une porte |

| de véhicule par le servomoteur via un RFID PN532                                      |

### LISTE DES ABREVIATIONS

| A                                                                                   |

|-------------------------------------------------------------------------------------|

| ASM: Algorithmic Sequential Machines ASIC: Application Specific Integrated Circuit. |

| CAO: Conception Assistée par Ordinateur.                                            |

| CLB: Configurable Logic Block.                                                      |

| CPLD: Complex Programmable Logic Device.                                            |

| CPU: Central Processing Unit                                                        |

| CMOS: Complementary Metal-Oxide-Semiconductor.                                      |

| D                                                                                   |

| DC: Direct Current.                                                                 |

| DSP: Digital Signal Processor.                                                      |

| DoD: Department of Defense (United States).                                         |

| F                                                                                   |

| FLASH: Flash Memory                                                                 |

| FPGA: Field Programmable Gate Arrays.                                               |

| FIFO: First In, First Out                                                           |

| G                                                                                   |

| GPU: Graphics Processing Unit                                                       |

| H                                                                                   |

| HDL: Hardware Description Language (language de description matériel)               |

$\textbf{HSYNCH}: \textbf{S} ynchronisation \ \textbf{H} orizontale$

| I                                                                                                                                                   |                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| IA: Intelligence Artificial                                                                                                                         |                     |

| IEEE: Institut of Electrical and Elec                                                                                                               | etronics Engineers. |

| IOB: Input Output Bloc.                                                                                                                             |                     |

| IEO: Element D'entrée/Sortie                                                                                                                        |                     |

| I2C: Inter-Integrated Circuit                                                                                                                       |                     |

| J                                                                                                                                                   |                     |

| JTAG: Joint Test Action Group                                                                                                                       |                     |

| L                                                                                                                                                   |                     |

| LAB: Logic Array Bloc.  LE: Elément Logique.  LUT: Look up Table.  LCD: Liquid Crystal Display  LED: Diode Electroluminescente  LC: Cellule Logique |                     |

| NFC: Near Field Communication P                                                                                                                     | -                   |

| PAL: Programmable Array Logic                                                                                                                       |                     |

| PLD: Programmable Logic Device                                                                                                                      |                     |

| PLL : Phase-Locked Loop                                                                                                                             |                     |

| PWM: Pulse Width Modulation                                                                                                                         |                     |

| RAM: Random Access Memoy.                                                                                                                           |                     |

| RFID: Radio Frequency Identification                                                                                                                |                     |

| ROM: Read-Only Memory                                                                                                                               |                     |

| RTL: Register Transfer Level.                                                                                                                       |                     |

| S                                                 |

|---------------------------------------------------|

| SDRAM: Synchronous Dynamic Random Access Memory   |

| SPLD: Simple Programmable Logic Device            |

| SRAM: Static Random Access Memory.                |

| SPI: Serial Peripheral Interface                  |

| T                                                 |

| TTL: Transistor-Transistor Logic                  |

| U                                                 |

| UART: Universal Asynchronous Receiver/Transmitter |

| UID: Unique Identifier                            |

| V                                                 |

| VHDL: VHSIC Hardware Description Language.        |

VHSIC: Very High Speed Integrated Circuit.

VLSI: Very Large Scale Integration.

## INTRODUCTION GENERALE

### INTRODUCTION GENERALE

Depuis la commercialisation du premier circuit programmable FPGA (Field Programmable Gate Arrays) en 1985, l'utilisation de ces circuits ne cesse de s'étendre à des domaines et applications variés, parmi lesquels nous pouvons citer le traitement d'image et de vidéos [1], [2], les réseaux de neurones [3], la comparaison de séquences génétiques [4], l'architecture des ordinateurs [5] etc... L'intérêt suscité par les FPGA est dû essentiellement à leurs prix abordables, facilité de mise en œuvre et flexibilité [6].

Parallèlement, l'évolution rapide des technologies embarquées et l'essor de l'intelligence artificielle (IA) ont renforcé le besoin en systèmes intelligents, autonomes et réactifs, notamment dans des domaines comme la robotique mobile, l'industrie ou la logistique automatisée. Dans ce contexte, les FPGA apparaissent comme une solution idéale pour concevoir des architectures matérielles parallèles et adaptables, capables de satisfaire des exigences strictes en matière de performance, de consommation et de traitement en temps réel.

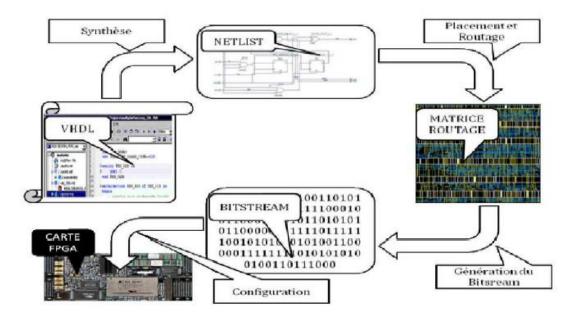

Pour réaliser une application avec un FPGA il faut décrire le circuit électronique à réaliser avec un langage de description matérielle comme le VHDL. Puis il faut synthétiser cette description en circuit électronique. Cette étape et les suivantes peuvent se faire avec des logiciels fournis par le fabricant de circuit. Enfin après une étape de placement et routage qui prend en compte l'architecture du FPGA, un fichier de configuration appelé *bitstream* est généré. Celui-ci permet de spécifier au FPGA lors de la configuration la position des points de la mémoire de configuration.

Le présent mémoire s'inscrit dans ce cadre et porte sur la conception et la réalisation d'un véhicule omnidirectionnel piloté par un FPGA de la famille Cyclone IV de type EP4CE10E22C8. Ce véhicule intègre plusieurs fonctions avancées combinant mobilité, perception de l'environnement et interaction intelligente. Il a pour but de démontrer comment le langage VHDL peut être exploité pour implémenter un système embarqué complet, englobant la lecture de

capteurs, le contrôle de moteurs, la communication sans fil, ainsi qu'un traitement logique simple et réactif.

Le véhicule développé fonctionne selon deux modes :

- ✓ Mode manuel, où l'utilisateur commande le déplacement via une application mobile Bluetooth, à l'aide d'un module HC-05.

- ✓ Mode autonome, où le véhicule réagit à son environnement à l'aide d'un capteur ultrasonique HC-SR04. Il mesure les distances, affiche les valeurs sur un écran LCD, active un buzzer en cas d'obstacle à moins de 30 cm, et prend des décisions comme tourner à gauche pour éviter la collision.

Parmi les interfaces de communication utilisées dans ce projet, le module RFID PN532 occupe une place importante. Il permet d'implémenter une méthode simple et efficace d'identification des utilisateurs via la technologie Radio Frequency Identification (RFID).

Le système RFID repose sur l'échange de données entre un lecteur et un tag (ou carte) à l'aide d'ondes radio. Lorsqu'un tag RFID entre dans la zone de détection du lecteur, ce dernier peut lire son identifiant unique (UID). Le module PN532 utilisé ici est compatible avec la norme NFC (Near Field Communication) et communique avec le FPGA via une interface série UART, bien adaptée aux architectures embarquées.

Dans le cadre de notre projet, ce système est utilisé pour sécuriser l'accès à la porte du véhicule. Si le tag présenté est reconnu comme autorisé, un servomoteur est activé pour permettre l'ouverture automatique de la porte. Cette solution présente l'avantage d'être sans contact, rapide et fiable, tout en offrant une couche de sécurité adaptée aux systèmes embarqués.

Cette fonctionnalité est particulièrement pertinente si le véhicule est envisagé comme un distributeur mobile (par exemple, pour la livraison de médicaments, d'outils ou de colis). Seuls les utilisateurs munis d'un badge ou d'une carte RFID autorisée peuvent alors accéder à son contenu, renforçant ainsi le contrôle d'accès dans des environnements partagés ou sensibles.

L'intégration du module RFID illustre non seulement l'exploitation d'un périphérique externe via une liaison série UART, mais aussi la mise en œuvre d'un comportement conditionnel basé sur une authentification, qui constitue une brique élémentaire d'une intelligence embarquée sur FPGA.

Le choix d'un véhicule omnidirectionnel, capable de se déplacer dans toutes les directions sans rotation préalable, améliore considérablement la manœuvrabilité, notamment dans des espaces restreints, ce qui est essentiel dans de nombreuses applications de robotique moderne.

Ce projet a permis de concrétiser les enseignements théoriques liés aux FPGA et au VHDL, tout en abordant des notions simples d'intelligence embarquée. Il ouvre également la voie à des perspectives d'amélioration, telles que l'intégration de modules de vision artificielle, de cartographie dynamique, ou d'algorithmes d'optimisation de trajectoire.

Ce mémoire se divise en trois chapitres organisés de la manière qui suit :

Dans le premier chapitre, nous nous intéressons aux circuits logiques programmables et en particulier les FPGA et plus spécialement les FPGA de la famille cyclone IV, en détaillant leurs caractéristiques et leurs avantages dans les systèmes embarqués.

Le deuxième chapitre, traite l'outil indispensable pour la programmation d'un FPGA qui est le langage VHDL et les fonctionnalités de base de celui-ci lors des phases de conception ou de synthèse. Ce chapitre aborde également des notions liées à la présentation des notions de base du système RFID utilisé dans le projet.

Le troisième chapitre est le cœur pratique du projet. Il présente la conception matérielle et logicielle. Il décrit le processus complet de conception et d'implémentation sur FPGA à l'aide de l'environnement Quartus II. Il présente la carte de développement FPGA utilisée, le matériel connecté, ainsi que les blocs VHDL développés (schémas fonctionnels RTL).

Dans un premier temps, nous allons afficher le message "WELCOME " sur un écran LCD pour l'accueil. Ensuite, nous avons utilisé un capteur ultrasonique pour mesurer la distance et afficher la valeur mesurée sur l'écran LCD. Lorsque

quelqu'un entre dans une zone de 30 cm, un buzzer s'active pour alerter de sa présence.

La conception et la réalisation de notre véhicule omnidirectionnel se divise en deux parties :

- ➤ Commande manuelle : création d'une application mobile (via MIT App Inventor) pour envoyer des commandes Bluetooth au FPGA, contrôle des moteurs pour un déplacement omnidirectionnel.

- Mode autonome : développement d'un système de prise de décision simple basé sur les mesures d'un capteur ultrasonique HC-SR04. Si la distance est inférieure à 30 cm, le véhicule active un buzzer et effectue une rotation à gauche.

Enfin, nous terminons notre travail avec une conclusion générale dressera le bilan de cette étude.

### REFERENCES BIBLIOGRAPHIQUES -INTRODUCTION-

- [1] S. C. Chan, H.O. Ngai and K.L. Ho, "A programmable image processing system FPGA" International journal of electronics, vol 75, N°4 pp 725-730, 1993. [2] M. Alves de barros, "Traitement bas niveau d'images en temps réel et circuits reconfigurables" Thèse de doctorat, Université Paris-Sud, de 1994. [3] J.G. Eldrerge, B.L. Hutchings, "Density enhancement of neural network using reconfiguration" **FPGAs** and run-time FCCM. 1994. [4] E. Lemoine, J. Quinqueton and J. Salantin, "High speed pattern matching in genetic data base with reconfigurable hardware" Proceeding of th 2nd INT. Conf. o, Intelligent AAAI, systems for molecular biology, pp 269-276. [5] B.Heeb and C. Pfister, "Chameleon, a workstation of a different colour" 2nd International Workshop on Field-Programmable Logic Applications, paper 5.6, Vienna, Austria, 1992. [6] H.Guermoud, Y.Berviller, E.Tisserand, S.Weber, « Architecture à base de

- [6] H.Guermoud, Y.Berviller, E.Tisserand, S.Weber, « Architecture à base de FPGA reconfigurable dynamiquement dédiée au traitement d'image sur flot de données », SEIZIÈME COLLOQUE GRETSI 15-19 SEPTEMBRE 1997 GRENOBLE

# Chapitre I Circuits logiques programmables FPGA

### I.1 Introduction

FPGA est l'abréviation de Field Programmable Gate Arrays ou "réseaux logiques programmables". Inventés par la société Xilinx en 1985, les FPGA sont des composants logiques de haute densité et reconfigurables qui permettent, après programmation, de réaliser des fonctions logiques, des calculs, et des générations de signaux. Il s'agit d'un circuit intégré qui peut être programmé pour fonctionner selon la conception prévue. Cela signifie qu'il peut fonctionner comme un microprocesseur, ou comme une unité de cryptage, ou une carte graphique, ou même tous ces trois à la fois.

L'avantage de ce genre de circuit est sa grande souplesse qui permet de les réutiliser à volonté dans des algorithmes différents en un temps très court. Les FPGAs peuvent être utilisés pour implémenter n'importe quelle fonction logique que les Circuits intégrés spécifiques ASICs (Application Specific Integrated Circuit) peuvent implémenter. Leur reconfiguration, qui peut être effectuée un nombre arbitraire de fois, représente l'un de leurs avantages majeurs par rapport aux ASICs [I.1], [I.2], [I.3].

Les conceptions fonctionnant sur des FPGA sont généralement créées à l'aide de langages de description de matériel tels que VHDL et Verilog.

Le présent chapitre décrit les FPGAs ainsi que les principaux composants et éléments qui les caractérisent, leurs avantages et différents domaines d'applications. En particulier, le FPGA de la famille Cyclone IV fait l'objet d'une présentation détaillée de ses composants et caractéristiques.

### I.2 Circuits Logiques Programmables du type FPGA

### I.2.1 Définition du FPGA

Les FPGA, sigle anglais qui signifie « Field Programmable Gates Arrays » traduit en français par réseau de portes programmables, sont des circuits intégrés reprogrammables. Ils offrent la possibilité de réaliser des fonctions numériques plus ou moins complexes, tout comme leurs homologues figés : les ASIC [I.4], [I.5], [I.6].

Figure I.1: Image d'un circuit FPGA [I.7].

Les FPGAs, sont des composants électroniques programmables de la famille des PLDs (**P**rogrammable **L**ogic **D**evice). Un FPGA est un ensemble de blocs logiques élémentaires que l'utilisateur peut interconnecter pour réaliser les fonctions logiques de son choix. La densité des portes est importante et sans cesse en évolution. L'avantage d'un FPGA est leur grande souples se dans leur technologie permettant une réutilisation à volonté et en un temps très court (quelques millisecondes) dans des algorithmes différents. Le progrès technologique permet de faire des composants toujours plus rapides et à plus haute intégration, autorisant la programmation d'applications importantes [I.8].

Grâce à l'évolution des procédés de fabrication, ces composants peuvent actuellement supporter des applications complexes. Ils sont constitués d'un réseau de blocs logiques, de blocs mémoires, de blocs dédiés et d'entrées/sorties. L'ensemble est relié par un réseau d'interconnexions programmable. Les blocs logiques permettent de réaliser des opérations avec quelques variables à travers une LUT (Look Up Table) [I.9]. Le résultat peut être éventuellement stocké dans un registre, les blocs RAM permettent d'implanter des mémoires adressables et des FIFO (First In, First Out), les blocs dédiés permettent de réaliser facilement de nombreuses opérations de traitement (blocs DSP), de gérer l'horloge, ou des interfaces de communication (Rocket IO, Ethernet, PCI Express). Les nombreux

ports permettent également de connecter des périphériques de la plateforme matérielle à base de FPGA.

Les FPGA se programment grâce à leurs LUT et leur réseau d'interconnexion. La programmation se fait avec un langage de programmation hardware tel que le VHDL ou bien le Verilog. L'outil de développement transforme cette description en un fichier de configuration du FPGA en plusieurs étapes : le HDL (Hardware Design Language) doit d'abord être synthétisé (transformé en éléments logiques de base), puis les éléments doivent être placés sur le composant (placement) et enfin interconnectés (routage) [I.10].

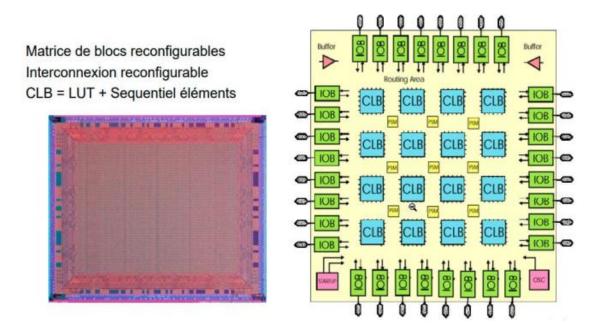

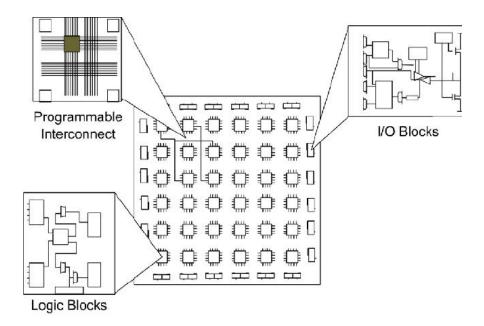

### I.2.2 Architecture [I.11]

Structurés sous forme de matrices, les FPGA sont composés d'éléments logiques de base, constitués de portes logiques, présentes physiquement sur le circuit. Ces portes sont reliées par un ensemble d'interconnexions modifiables : d'où l'aspect programmable du circuit.

Figure I.2: Architecture interne des FPGAs

Figure I.3 : Différents secteurs d'un FPGA

La structure du FPGA présentée figure I.2 est composée :

- ❖ De cellules d'entrées sorties modifiables qui servent d'interfaces entre les broches du circuit et le cœur du FPGA pour adapter les signaux suivants :

- Alimentation

- Signaux d'horloge

- Signaux de configuration du FPGA

- Signaux de test

- ❖ De blocs logiques ou éléments logiques contenant les fonctions logiques combinatoires et séquentielles.

- La partie combinatoire permet de réaliser des fonctions de complexité moyenne avec des portes classiques ET, OU et NON de deux à une dizaine d'entrées.

- La partie séquentielle comporte une ou deux bascules généralement de type

D.

Compte tenu du nombre d'éléments logiques et de leur structure, leur association permet de réaliser tous les types de bascule. L'intérêt est de créer des mémoires élémentaires à un bit.

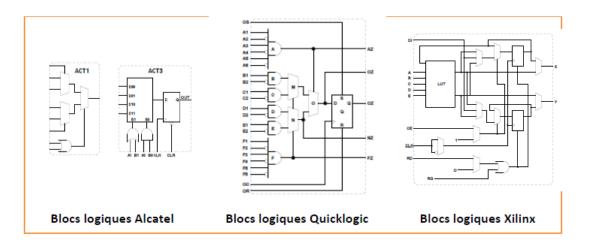

Suivant le fabricant du circuit, ces blocs contiennent un nombre différent de portes logiques et de bascules à l'intérieur d'un bloc comme le montre la figure I.4.

Figure I.4 : Exemple de blocs logiques de différents fabricants.

Il existe 4 types de blocs logiques :

Les macro-cellules : Ces cellules logique sont appelé aussi par :

- ✓ Soit CLB (configurable logique bloc), dénomination adoptée par XILINX.

- ✓ Soit LC (cellule logique), le nom choisi par CYPRESS.

- ✓ Soit LE (élément logique), l'appellation d'ALTERA.

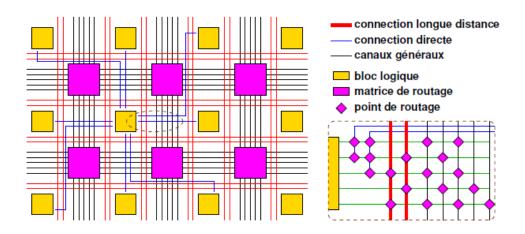

- ❖ De réseaux d'interconnexions que l'on voit en figure I.5. Ces réseaux relient entre eux les blocs logiques et les blocs d'entrées/sorties. Ces connections peuvent directement relier :

- Des éléments internes dans un bloc grâce à un système de tables logiques appelées LUT. C'est une matrice de connections où les points de routage déterminent le niveau des entrées soit haut soit bas des portes logiques.

- **Des éléments proches** : on parle de liaisons directes entre les blocs.

Plusieurs blocs présents sur toute la surface : on parle de liaisons à distance ou générales.

Certains de ses canaux sont spécifiques aux signaux d'horloges.

Figure I.5 : Structure générale du routage

**Remarque:** L'échelle est fausse (blocs logiques < 5% du circuit).

Un microprocesseur : La présence d'un processeur est indispensable pour ordonnancer les commandes reçues par le FPGA. C'est le chef d'orchestre de tout système informatique, où son rôle est de suivre des instructions qui lui ont été préalablement programmées en langage C.

Habituellement, ce processeur se trouve à l'extérieur du FPGA, mais des constructeurs ont intégré ces systèmes directement dans le FPGA. Il s'agit de processeur « soft-core » (soft pour logiciel et core pour cœur d'exécution) on parle aussi de système sur puce programmable (SOPC) (System On Programmable Chip). Il communique avec le FPGA grâce au langage de description matérielle VHDL. Ce processeur est donc reconfigurable pouvant ainsi d'adapter aux contraintes de chaque utilisation.

### **ASICs**

Dans la littérature, le terme ASIC (Application Specific Integrated Circuit) est employé pour décrire l'ensemble des circuits spécifiques à une application. Or,

dans le langage courant, le terme ASIC est presque toujours utilisé pour décrire les circuits réalisés chez un fondeur. On désigne, par le terme générique PLD (Programmable logic Device), l'ensemble des circuits programmables par l'utilisateur.

### I.2.3 FPGAs: illustration avec la famille Cyclone IV d'Altera

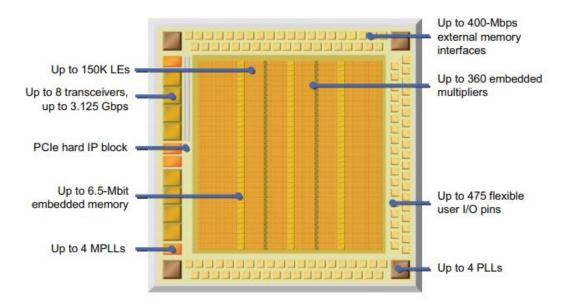

S'appuyant sur le succès des FPGA Cyclone et pour accroître son leadership sur les interfaces haut débit, Altera Corporation présente sa nouvelle gamme de FPGA Cyclone IV. Afin de répondre à l'augmentation des besoins en bande passante au moindre coût provoquée par la demande en vidéo mobile, en voix, en accès aux données et en images 3D de qualité, la nouvelle gamme de FPGA Cyclone IV ajoute la prise en charge des protocoles série standards et offre le meilleur compromis en coût, puissance et en fonctionnalités logiques, mémoire et DSP [I.11].

Figure I.6: Symbole de Cyclone IV d'Altera.

La gamme de FPGA Cyclone IV offre deux variantes. Les circuits Cyclone IV GX possèdent jusqu'à 150K éléments logiques, 6.5Mbits de RAM, 360 multiplieurs et 8 interfaces haut débit. Avec une basse consommation et un boitier de 11x11 mm seulement, ces circuits conviennent aux applications à taille réduite et

à faible coût des marchés sans fil, filaire, télédiffusion, industriel et grand public. Les circuits Cyclone IV E associent faible coût et hautes fonctionnalités et diminuent d'au moins de 25% la consommation par rapport à la génération précédente de FPGA Cyclone dans les applications basse consommation comme la radio logicielle portable [I.11].

Figure I.7: Caractéristiques architecturales clés du FPGA Cyclone IV [I.12].

L'architecture de Cyclone IV E comprend jusqu'à 115 K éléments logiques disposés verticalement (LE).

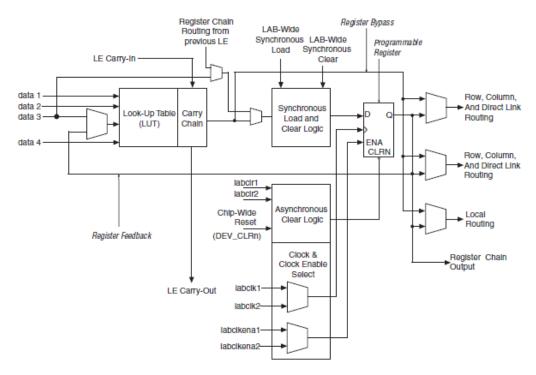

### **SEL** Elément logique (LE) Cyclone IV

C'est le plus petit élément de logique dans le Cyclone IV. Sa structure apparaît sur la figure ci-dessous :

**Figure I.8 :** Structure d'un Logic Element LE [I.13].

Cette cellule reconfigurable contient divers éléments :

- Une LUT (Look up table) à quatre entrées, permettant le calcul de n'importe quelle fonction de 4 entrées.

- Un registre de sortie programmable

- Une connexion de chaîne de transport

- Une connexion de chaîne de registre

- La possibilité de piloter les interconnexions suivantes :

- ✓ Locale

- ✓ Ligne

- ✓ Colonne

- ✓ Chaîne d'enregistrement

- ✓ Lien direct

- Enregistrez le support d'emballage

- Enregistrez le support de rétroaction

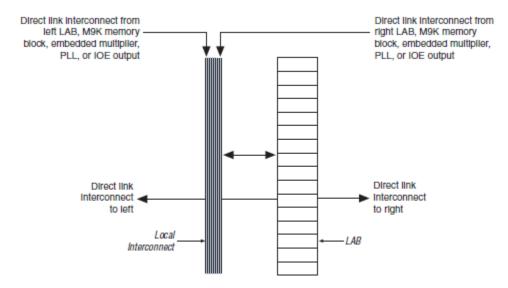

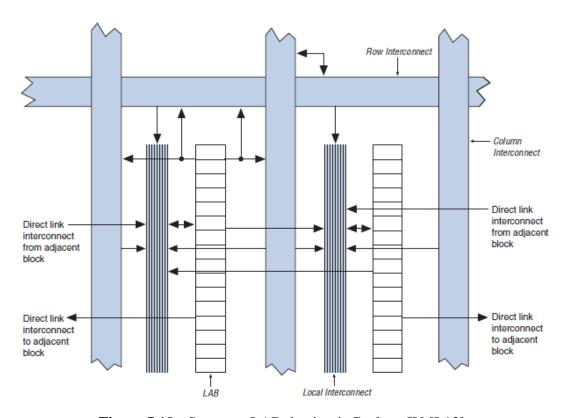

# **Blocs de réseaux logiques (LAB)**

Un bloc de réseaux logiques contient :

- 16 Eléments Logiques (LE).

- Un réseau d'interconnexion local pour la communication entre LE du même

LAB (voir figure I.9).

- Un accès direct aux éléments adjacents du LAB dans la structure du FPGA (voir figure I.9) tels que :

- ✓ un autre LAB.

- ✓ un bloc mémoire pour les LAB adjacents aux zones mémoires.

- ✓ un signal d'horloge d'une PLL.

- ✓ un multiplexeur.

- ✓ un IOE (Elément d'entrée/sortie).

- ✓ un accès aux réseaux d'interconnexions lignes/colonnes pour atteindre n'importe quel point du composant.

L'interconnexion locale LAB est pilotée par des interconnexions de colonne et de ligne et des sorties LE dans le même LAB. Les LAB voisins, les boucles à verrouillage de phase (PLL), les blocs de RAM M9K et les multiplicateurs intégrés de gauche et de droite peuvent également piloter l'interconnexion locale d'un LAB via la connexion de liaison directe. La fonction de connexion directe minimise l'utilisation d'interconnexions de lignes et de colonnes, offrant des performances et une flexibilité supérieures. Chaque LE peut piloter jusqu'à 48 LE via des interconnexions de liaison locales et directes rapides.

Le compilateur Quartus II place la logique associée dans un LAB ou des LAB adjacents, permettant l'utilisation de connexions de chaînes locales et de registres pour les performances et l'efficacité de la zone.

Figure I.9: Connexions chaînées entre LEs dans un LAB de circuit Cyclone IV [I.13].

Figure I.10: Structure LAB de circuit Cyclone IV [I.13].

# **❖** Bloc d'entrée/sortie (IOE : Input Output Element)

Avec l'accroissement constant du nombre de standards d'entrées/sorties en électronique numérique, la conception d'un FPGA a progressivement nécessité de faire apparaître des blocs dédiés capables d'interfaçages s'adaptant à une grande diversité de situation.

La frange supérieure des composants de la famille Cyclone IV dispose donc de nombreux blocs d'entrées/sorties (I/O Banks) répartis à la périphérie du composant.

La famille Cyclone IV peut s'interfacer avec des circuits logiques :

- LVTTL et LVCMOS : Interfaçage avec des circuits logiques d'usage général, fonctionnant à des fréquences moins de 100MHz.

- SSTL : Standard mis en place pour la mémoire SDRAM DDR (Double Data Rate).

- ➤ HSTL : Signaux des mémoires QDR2 SRAM (Quad Data Rate).

- ➤ LVDS (Low Voltage Differential Signaling) : Signaux différentiels (ils garantissent une plus grande immunité au bruit) pour des communications à fort débit (jusqu'à 805Mbps) et faible EMI (émissions électromagnétiques)

- ➤ LVPECL (Low Voltage Positive Emitter Coupled Logic) : Signaux différentiels à haute immunité au bruit utilisé en vidéo, télécom, distribution d'horloge.

- ➤ PCI et PCI Express Bus locaux des PC utilisés pour la connexion de car te d'extension (Vidéo . . .).

#### **Blocs de mémoire dans les appareils Cyclone IV**

Les dispositifs Cyclone IV présentent des structures de mémoire intégrées pour répondre aux besoins de mémoire sur puce des conceptions de dispositifs Altera Cyclone IV. La structure de mémoire intégrée se compose de colonnes de blocs de mémoire M9K que vous pouvez configurer pour fournir diverses fonctions de mémoire, telles que la RAM, les registres à décalage, la ROM et les buffers FIFO.

Les blocs M9K prennent en charge les fonctionnalités suivantes :

- 8 192 bits de mémoire par bloc (9 216 bits par bloc, parité comprise)

- Signaux d'activation de lecture (rden) et d'activation d'écriture (wren) indépendants pour chaque port

- Mode compact dans lequel le bloc de mémoire M9K est divisé en deux RAM à port unique de 4,5 Ko

- Configurations de ports variables

- Prise en charge des modes simple port et double port pour toutes les largeurs de port

- Véritable fonctionnement à deux ports (une lecture et une écriture, deux lectures ou deux écritures)

- L'octet active le masquage d'entrée de données pendant les écritures

- Deux signaux de contrôle d'activation d'horloge pour chaque port (port A et port B)

- Fichier d'initialisation pour pré-charger le contenu de la mémoire en modes RAM et ROM

**PLL:** Les boucles à verrouillage de phase (PLL : Phase Locked Loops) d'un Cyclone IV fournit une capacité de synthétiser une horloge principale qui permet la génération de plusieurs horloges internes qui fonctionnent à différentes fréquences issue de l'horloge d'entrée. Chaque PLL peut fournir jusqu'à trois sorties d'horloge pouvant fonctionner à des fréquences différentes. Le PLL est un système qui permet de synchroniser la phase instantanée de deux signaux.

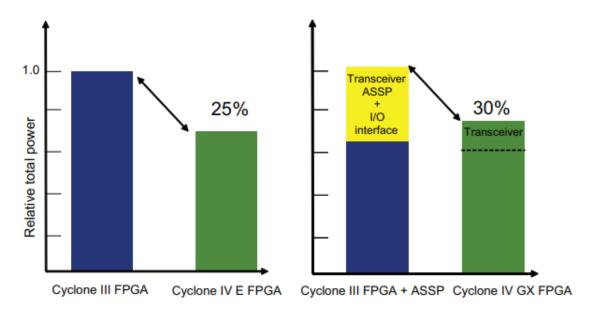

#### I.2.3.1 Puissance de circuit Cyclone IV

Comme le montre la figure I.11, Altera a travaillé avec son partenaire de fabrication de longue date TSMC pour optimiser le processus de fabrication afin de produire des FPGA avec une puissance statique et dynamique inférieure, jusqu'à 25 % et 30 % de puissance totale en moins respectivement par rapport aux familles Cyclone précédentes [I.14].

Figure I.11: Puissance Cyclone IV E (à gauche) et Cyclone IV GX (à droite) [I.14].

Les FPGA sont synonymes de commercialisation rapide des produits en raccourcissant le calendrier de développement des produits.

Les ingénieurs qui choisissent les FPGA Cyclone IV, avec des performances de cœur jusqu'à 25 % plus rapides (par rapport aux FPGA à faible coût des concurrents), consacreront moins d'itérations de conception à la fermeture temporelle, car une plus grande marge temporelle est disponible. De plus, le logiciel de conception Quartus II d'Altera a des temps de compilation jusqu'à 50 % plus rapides par rapport aux produits logiciels concurrents, ce qui rend les ingénieurs plus productifs, chaque jour au bureau [I.14].

#### I.2 .3.2 Programmation d'un périphérique de configuration série

Le dispositif Cyclone IV E prend en charge la programmation dans le système d'un dispositif de configuration série à l'aide de l'interface JTAG via la conception du chargeur flash série. Le chargeur flash série est une conception de pont pour l'appareil Cyclone IV E qui utilise son interface JTAG pour accéder au fichier EPCS .jic, puis utilise l'interface AS pour programmer l'appareil EPCS. La figure I.12 illustre la méthode de programmation lors de l'adoption d'une solution de chargeur flash série [I.15].

**Figure I.12 :** Programmation d'un périphérique de configuration série avec une solution de chargeur flash série [I.15].

# I.2 .3.3 Caractéristiques de Cyclone IV EP4CE10 FPGA [I.16]

- ✓ éléments logiques (EL) 10000

- ✓ Boucles de structure et d'E/S à phase asservie (PLL) 2

- ✓ Mémoire embarquée maximale 414 Kb

- ✓ Blocs DSP (Digital Signal Processing) 23

- ✓ Format DSP (Digital Signal Processing) Multiply

- ✓ Contrôleurs de mémoire matériels :Non

- ✓ Support mémoire externe (EMIF) DDR, DDR2, SDR

- ✓ Configuration E/S Nombre maximal d'utilisateurs des E/S 179

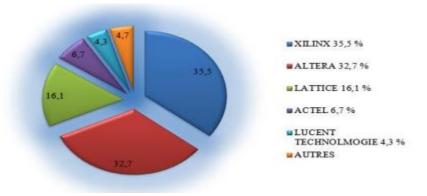

#### I.3 Principaux fondeurs d'FPGA

Les fabricants des FPGA ne cessent pas d'améliorer leurs produits par l'efficacité et la puissance. L'ensemble des firmes (Principaux fondeurs) qui conçoivent ce type de circuits sont : Altera, Actel, Atmel, Cypress, Lattice, Minc, QuicLogic, Xilinx et d'autres [I.17].

Figure I.13: Statistiques du marché occupé par les vendeurs d'FPGA [I.18].

# I.4 Configuration et reconfiguration des FPGA