الجامعة الجزائرية الديمقراطية الشعبية

REPUBLIQUE ALGERIENNE DEMOCRATIQUE ET POPULAIRE

وزارة التعليم العالي و البحث العلمي

Ministère de l'Enseignement Supérieur et de la Recherche Scientifique

جامعة الدكتور الطاهر مولاي سعيدة

Université Saida Dr Tahar Moulay –

Faculté de TECHNOLOGIE

## MEMOIRE

Projet de recherche présenté pour l'obtention du Diplôme de MASTER

En : Électronique

Spécialité : Instrumentation

### Sujet

**Génération de signaux vidéo VGA avec un FPGA pour les systèmes de vision artificielle**

Présenté par : SIRAT Abdelhak & BAHLOULI Hichem

Soutenue publiquement, Juin 2024, devant le jury composé de :

**Mr. BELLIL Ameur**

MCB

Univ. Saida

Président

**Melle. SEGHIER Salima**

MCB

Univ. Saida

Encadrant

**Melle. MAACHOU Fatima**

MCB

Univ. Saida

Examinateuse

# **Remerciements**

*Je remercie d'abord «Allah » qui m'a donné la force et le courage pour terminer mes études et élaborer ce modeste travail.*

*Ce travail n'aurait certainement jamais vu le jour sans l'aide, le soutien et le dévouement de certaines personnes que nous tiennent à remercier.*

*Nous remercions notre encadreur Dr. SEGHIER Salima, qui m'a fait bénéficier de son savoir, de ses compétences scientifiques et de sa passiance pour la recherche.*

*Nos remerciements les plus vifs s'adressent aux membres du jury d'avoir accepté d'examiner et d'évaluer notre travail.*

*Nos remerciements également à Mr A.ABDOUN l'ingénieur de laboratoire de FPGA.*

*Un grand remerciement à nos parents qui ont sacrifié pour nous, car grâce à leurs efforts nous sommes là.*

*Nos remerciements les plus sincères à toutes les personnes qui nous ont aidé dans ce mémoire même avec une simple sourire.*

# Dédicaces

*Je Dédié ce travail :*

*A ma très chère mère*

*A mon très cher père*

*Qui ont sacrifié leur vie pour*

*Ma réussite et m'ont éclairé le chemin par*

*Leurs conseils judicieux.*

*J'espère qu'un jour,*

*Je pourrai leurs rendre un peu de ce qu'ils*

*Ont fait pour moi, que dieu leurs prête bonheur et longue vie.*

*A mon grand-père et ma grand-mère*

*A mon encadreur Dr SGHIER SALIMA*

*A Mon binôme « BAHLOULI Hichem » avec qui j'ai passé des

agrables moments.*

*A ceux qui me sont chers*

*A ceux qui ont toujours cru en moi*

*A ceux qui m'ont toujours encouragé*

*A ma famille et mes meilleurs amis qui par leurs prières et

leurs encouragements, on a pu surmonter tout les obstacles.*

*A tous ceux qui m'aiment, et tous ceux que j'aime.*

**SIRAT ABDELHAK**

# Dédicaces

*Je Dédié ce travail :*

*A ma très chère mère*

*A mon très cher père*

*Qui ont sacrifié leur vie pour*

*Ma réussite et m'ont éclairé le chemin par*

*Leurs conseils judicieux.*

*J'espère qu'un jour,*

*Je pourrai leurs rendre un peu de ce qu'ils*

*Ont fait pour moi, que dieu leurs prête bonheur et longue vie.*

*A mon grand-père et ma grand-mère*

*A mon encadreur Dr SGHEIR SALIMA*

*A Mon binôme « SIRAT ABDELHAK » avec qui j'ai passé des

agrables moments.*

*A ceux qui me sont chers*

*A ceux qui ont toujours cru en moi*

*A ceux qui m'ont toujours encouragé*

*A ma famille et mes meilleurs amis qui par leurs prières et leurs

encouragements, on a pu surmonter tout les obstacles.*

*A tous ceux qui m'aiment, et tous ceux que j'aime.*

*À ceux avec qui j'étais uni par des liens familiaux, à ceux avec qui

je partageais les douceurs et les amers de la vie, « ma précieuse

famille », de la petite à la grande.*

*À ceux dont vous avez renforcé le soutien à travers moi, mon frère

et ma sœur*

*Aux mains cachées, à celles qui sont loin, aux plus proches en

esprit de ceux qui ont été mon aide et mon soutien, que Dieu les

bénisse et les protège... À toutes les connaissances qui m'ont

encouragé, même avec le sourire.*

*Que Dieu vous récompense bien et vous récompense avec la

meilleure récompense*

**BAHLOULI HICHEM**

## **RESUME:**

Les FPGAs (Field Programmable Gate Arrays) sont des circuits électroniques parallèles qui permettent aujourd’hui de développer des applications de plus en plus performantes en vitesse d’exécution et gourmandes en ressources matérielles. Dans notre projet, nous avons utilisé une caméra CMOS OV7670 pour capturer des images en temps réel et les afficher sur un écran VGA. Bien que notre projet n’implémente pas directement la vision artificielle, l’utilisation de la caméra et l’affichage des images en temps réel posent les bases pour une future intégration de systèmes de vision artificielle. En ajoutant des algorithmes de vision par ordinateur, notre système pourrait être amélioré pour non seulement capturer et afficher des images, mais aussi d’analyser et interpréter les scènes visuelles pour identifier des objets ou des situations spécifiques, augmentant ainsi les capacités de surveillance et d’alerte. Afin de réaliser la conception et l’implémentation de quelques fonctions d’affichages VGA, on a utilisé le langage de description matériel VHDL après avoir expliqué ses notions et ses fonctionnalités. Après, avoir implanté les programmes des différentes fonctions des signaux vidéo VGA sur FPGA dans l’environnement Quartus II, qui est un logiciel développé par la société ALTERA permettant la gestion complète d’un flot de conception, on a finalement générée nos signaux de caractères et des images sur un écran vidéo VGA.

## **MOTS CLES:**

FPGA, VHDL, implémentation, RVB, pixels, VGA, génération des signaux, Cyclone IV, vision artificielle, logiciel Qartus II.

## **Abstract:**

FPGAs (Field Programmable Gate Arrays) are parallel electronic circuits which today make it possible to develop applications that are increasingly efficient in execution speed and demanding in hardware resources. In our project, we used an OV7670 CMOS camera to capture real-time images and display them on a VGA screen. Although our project does not directly implement artificial vision, the use of the camera and the display of images in real time lays the foundation for future integration of artificial vision systems. By adding computer vision algorithms, our system could be enhanced to not only capture and display images, but also analyze and interpret visual scenes to identify specific objects or situations, thereby increasing surveillance and monitoring capabilities. 'alert. In order to design and implement some VGA display functions, we used the VHDL hardware description language after explaining its concepts and functionalities. After having implemented the programs for the different functions of the VGA video signals on FPGA in the Quartus II environment, which is software developed by the company ALTERA allowing the complete management of a design flow, we finally generated our character signals and images on a VGA video display.

## **Keywords:**

FPGA, VHDL, implementation, RGB, pixels, VGA, signal generation, Cyclone IV, artificial vision, Qartus II software.

## **ملخص:**

(مصفوفات البوابات القابلة للبرمجة) عبارة عن دوائر إلكترونية متوازية تتيح اليوم إمكانية تطوير تطبيقات ذات كفاءة متزايدة في سرعة التنفيذ وتتطلب موارد الأجهزة. في مشروعنا، استخدمنا كاميرا OV7670 CMOS لالتقاط صور في الوقت الفعلي وعرضها على شاشة VGA. على الرغم من أن مشروعنا لا ينفذ الرؤية الآلية بشكل مباشر، إلا أن استخدام الكاميرا وعرض الصور في الوقت الفعلي يضع الأساس للتكامل المستقبلي لأنظمة الرؤية الآلية. ومن خلال إضافة خوارزميات رؤية الكمبيوتر، يمكن تحسين نظامنا ليس فقط لالتقاط الصور وعرضها، ولكن أيضًا لتحليل وتقدير المشاهد المرئية لتحديد أشياء أو مواقف معينة، وبالتالي زيادة قدرات المراقبة والمراقبة. من أجل تصميم وتنفيذ بعض وظائف عرض VGA، استخدمنا لغة وصف الأجهزة VHDL بعد شرح مفاهيمها ووظائفها. بعد تنفيذ البرامج الخاصة بالوظائف المختلفة لإشارات فيديو VGA على بيئة Quartus II FPGA، وهو برنامج تم تطويره بواسطة شركة ALTERA يسمح بالإدارة الكاملة لتدفق التصميم، فمنا أخيرًا بإنشاء إشارات وصور شخصيتنا على VGA عرض الفيديو.

## **الكلمات الدالة:**

.Qartus II، VHDL، FPGA، التتنفيذ، RGB، البكسلات، VGA، توليد الإشارة، Cyclone IV، الرؤية الاصطناعية، برنامج

## **SOMMAIRE**

**Remerciement**

**Dédicace**

**Résumé**

**Sommaire**

**Liste des Figures**

**Liste des Tableaux**

**Liste D'abréviation**

**Introduction Générale .....** ..... 1

### **Chapitre I : Circuits logiques programmables FPGA**

|                                                                                                   |    |

|---------------------------------------------------------------------------------------------------|----|

| <b>I.1 Introduction .....</b>                                                                     | 4  |

| <b>I.2 Circuits Logiques Programmables du type FPGA .....</b>                                     | 4  |

| I.2.1 Architecture .....                                                                          | 6  |

| I.2 .2 FPGAs : illustration avec la famille Cyclone IV d'Altera .....                             | 10 |

| I.2 .2.1 Puissance de circuit Cyclone IV .....                                                    | 16 |

| I.2 .2.2 Programmation d'un périphérique de configuration série .....                             | 17 |

| I.2 .2.3 Caractéristiques de Cyclone IV EP4CE10 FPGA .....                                        | 18 |

| <b>I.3 Avantages du FPGA .....</b>                                                                | 18 |

| <b>I.4 Critères de choix du circuit programmable FPGA.....</b>                                    | 19 |

| <b>I.5 Principaux fondeurs d'FPGA .....</b>                                                       | 20 |

| <b>I.6 Configuration et reconfiguration des FPGA .....</b>                                        | 21 |

| <b>I.7 Méthodologie de conception.....</b>                                                        | 21 |

| I.7.1 Outils de CAO (Conception Assistée par Ordinateur) pour la configuration<br>d'un FPGA ..... | 21 |

| I.7.1.1 Spécification du design .....                                                             | 22 |

| I.7.1.2 Développement du design .....                                                             | 22 |

| I.7.1.3 Synthèse .....                                                                            | 23 |

| I.7.1.4 Placement et routage.....                                                                 | 23 |

|                                                                     |           |

|---------------------------------------------------------------------|-----------|

| I.7.1.5 Intégration et implémentation .....                         | 24        |

| I.8 Principales applications des FPGA .....                         | 24        |

| I.9 Rapide présentation de la carte de développement d'Altera ..... | 25        |

| I.9.1 Caractéristiques de notre composant FPGAEP4CE10E22C8.....     | 25        |

| I.9.2 Différentes parties de la carte OMDAZZ.....                   | 26        |

| I.10 Conclusion.....                                                | 27        |

| <b>Références Bibliographiques Chapitre I.....</b>                  | <b>28</b> |

**Chapitre II : Présentation de VHDL, signal vidéo VGA et la vision

artificielle**

|                                                                            |           |

|----------------------------------------------------------------------------|-----------|

| <b>II.1 Introduction .....</b>                                             | <b>30</b> |

| <b>II.2 Langages de description matérielle .....</b>                       | <b>31</b> |

| II.2.1 Historique .....                                                    | 31        |

| II.2.2 Langages HDL.....                                                   | 32        |

| II.2.3 Langage de description matérielle VHDL .....                        | 32        |

| II.2.3.1 Structure d'un programme VHDL.....                                | 33        |

| II.2.3.1.1 Entête.....                                                     | 34        |

| II.2.3.1.2 Déclaration des librairies .....                                | 34        |

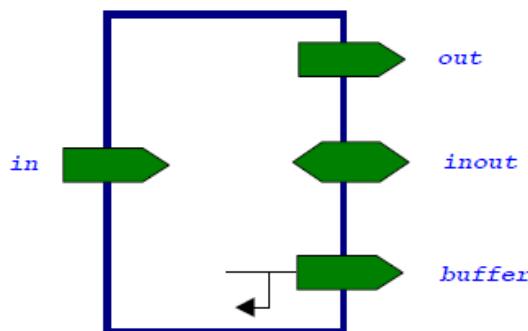

| II.2.3.1.3 Déclaration d'entité .....                                      | 35        |

| II.2.3.1.4 Signal d'entré/sortie .....                                     | 36        |

| II.2.3.1.4 Architectures .....                                             | 37        |

| II.2.3.1.4.1 Description comportementale.....                              | 38        |

| II.2.3.1.4.2 Description structurelle.....                                 | 39        |

| II.2.3.1.4.3 Description mixte .....                                       | 40        |

| II.2.3.1.4 Relation entre une structure VHDL et un circuit numérique ..... | 40        |

| II.2.4 Types d'instructions utilisées en VHDL.....                         | 41        |

| II.2.4.1 Instructions concurrentes .....                                   | 41        |

| II.2.4.1.1 Affectation simple.....                                         | 42        |

| II.2.4.1.2 Affectation conditionnelle.....                                 | 42        |

| II.2.4.1.3 Affectation sélective .....                                     | 42        |

|                                                                                           |           |

|-------------------------------------------------------------------------------------------|-----------|

| II.2.4.1.4 Instanciation du composant .....                                               | 43        |

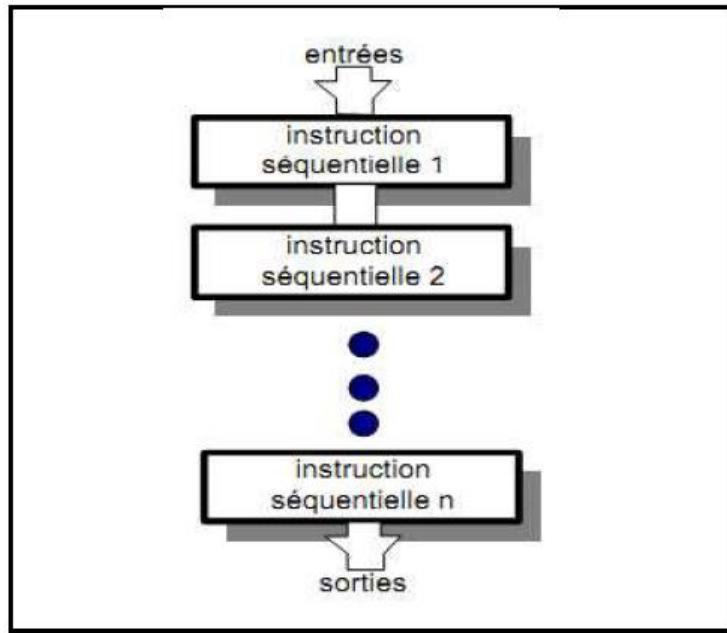

| II.2.4.2 Instructions séquentielles .....                                                 | 43        |

| II.2.4.2.1 Définition d'un process .....                                                  | 43        |

| II.2.4.2.2 Principales instructions utilisées dans un process .....                       | 44        |

| II.2.4.2.2.1 Instruction conditionnelle .....                                             | 44        |

| II.2.4.2.2.2 Instruction de choix.....                                                    | 45        |

| II.2.4.2.2.3 Instruction wait .....                                                       | 45        |

| II.2.4.2.2.4 Boucles .....                                                                | 45        |

| II.2.5 Opérateurs de base .....                                                           | 46        |

| II.2.5.1 Opérations logiques .....                                                        | 46        |

| II.2.5.2 Opérations relationnelles.....                                                   | 47        |

| II.2.5.3 Opérations d'addition .....                                                      | 47        |

| II.2.5.4 Opérations de signe.....                                                         | 47        |

| II.2.5.5 Opérations de multiplication .....                                               | 47        |

| II.2.5.6 Opérations NOT, ABS et ** .....                                                  | 48        |

| II.2.5.7 Sous programmes .....                                                            | 48        |

| II.2.5.7.1 Fonctions .....                                                                | 48        |

| II.2.5.7.2 Procédures .....                                                               | 49        |

| II.2.6 Différences entre VHDL et un langage de programmation .....                        | 50        |

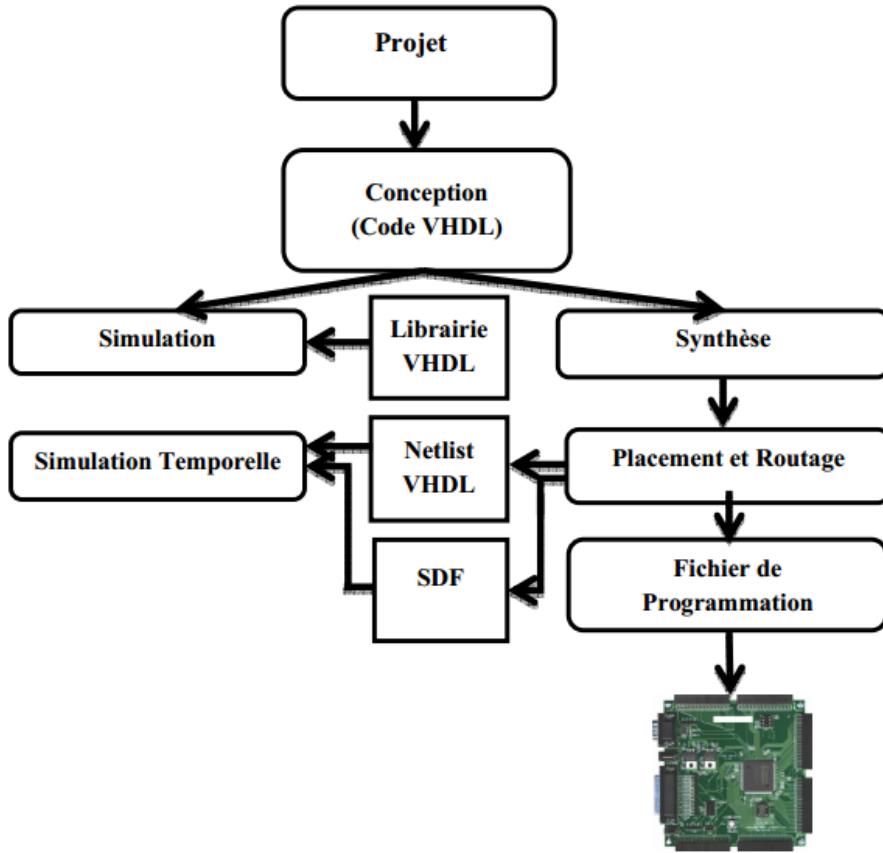

| II.2.7 Vérification d'une conception VHDL .....                                           | 50        |

| II.2.8 Développement d'un projet en VHDL.....                                             | 51        |

| <b>II.3 Généralités sur les images .....</b>                                              | <b>52</b> |

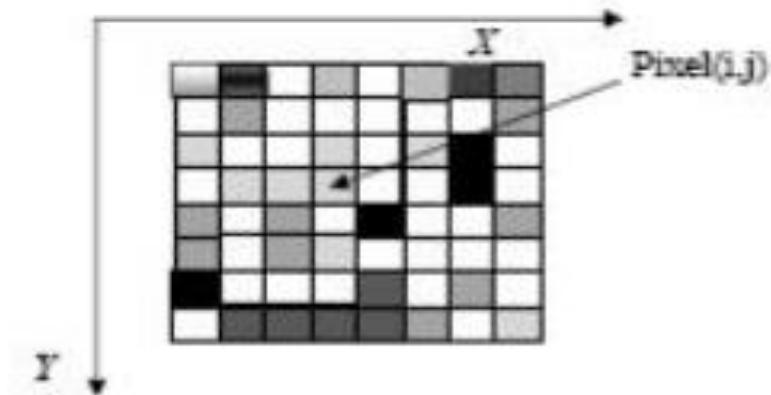

| II.3.1 Définition de l'image .....                                                        | 52        |

| II.3.2 Image numérique .....                                                              | 53        |

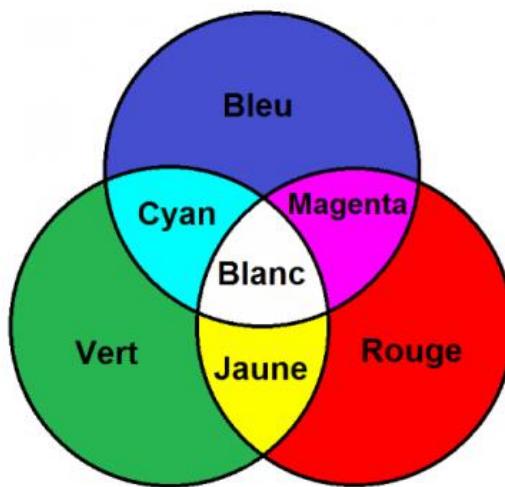

| II.3.3 Définition de l'espace de couleurs.....                                            | 54        |

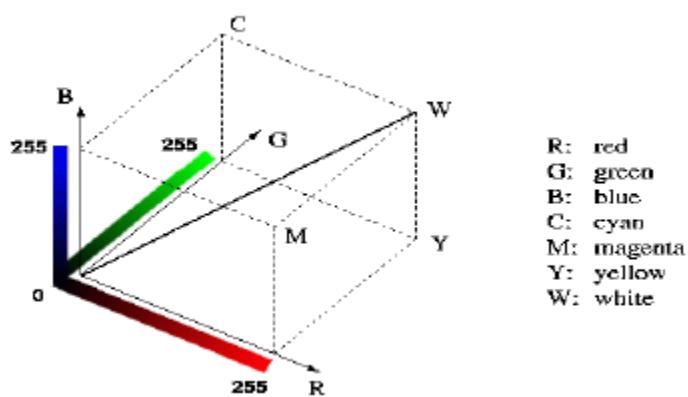

| II.3.3.1 L'espace RGB.....                                                                | 54        |

| II.3.4 Mécanique d'affichage d'une image.....                                             | 56        |

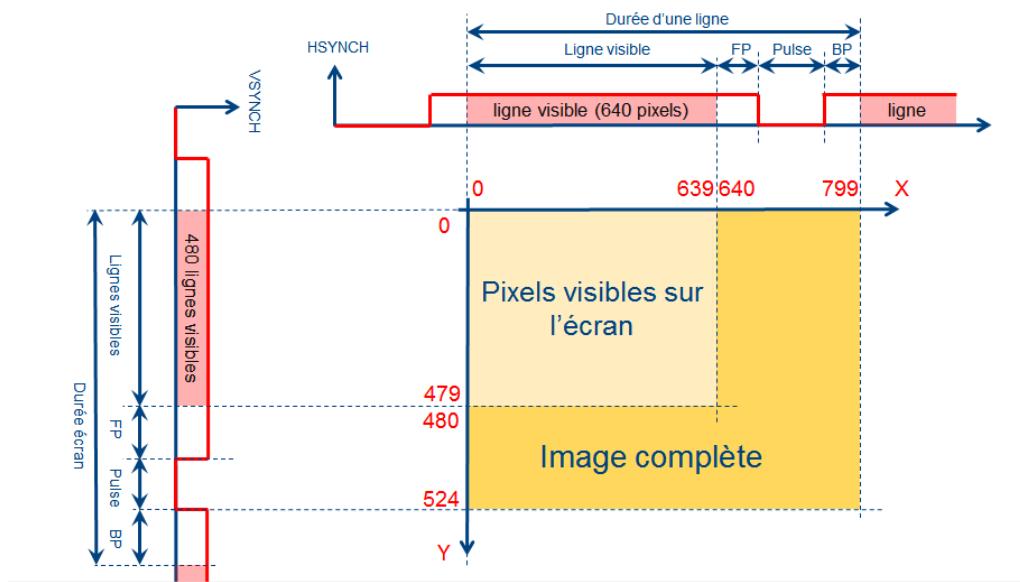

| II.3.4.1 Le signal vidéo VGA .....                                                        | 56        |

| II.3.4.2 L'affichage VGA et la génération des signaux de synchronisation de l'image ..... | 56        |

| II.3.4.3 Génération d'affichage vidéo VGA à l'aide de FPGA .....                          | 58        |

|                                                                                       |           |

|---------------------------------------------------------------------------------------|-----------|

| II.3.4.3.1 Technologie d'affichage vidéo.....                                         | 58        |

| II.3.4.3.2 Rafraîchissement de la vidéo.....                                          | 60        |

| <b>II.4 La Vision artificielle.....</b>                                               | <b>62</b> |

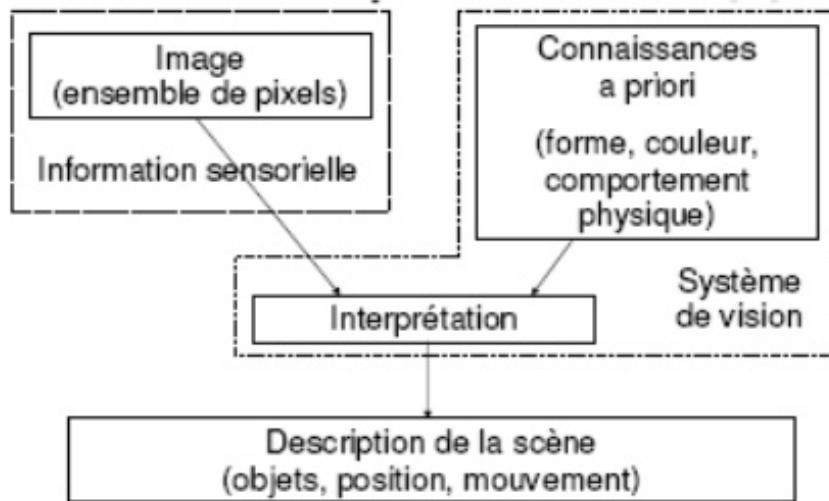

| II.4.1 Vision et système de vision .....                                              | 62        |

| II.4.2 Définition de la vision artificielle .....                                     | 63        |

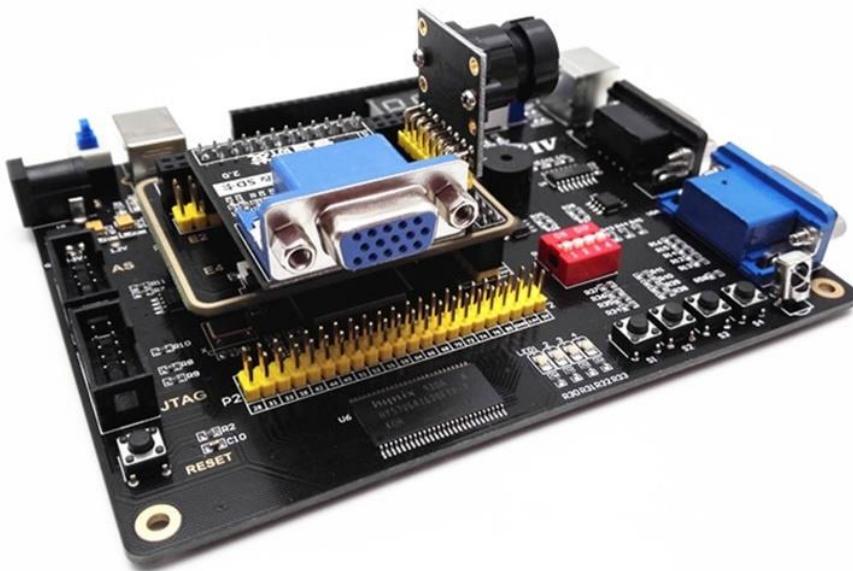

| <b>II.5 Montage de la caméra et le module VGA avec la carte FPGA Cyclone IV .....</b> | <b>63</b> |

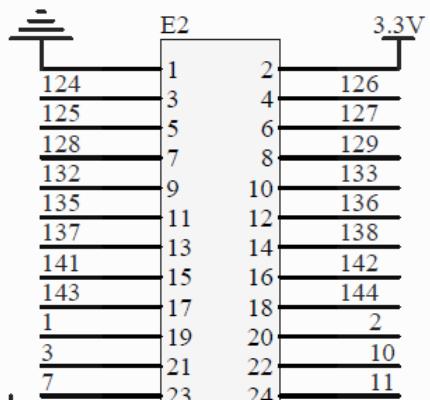

| II.5.1 Carte de connexion .....                                                       | 64        |

| II.5.2 Module VGA.....                                                                | 64        |

| II.5.3 Module caméra OV7670 .....                                                     | 65        |

| II.6 Conclusion .....                                                                 | 68        |

| <b>Références Bibliographiques Chapitre II .....</b>                                  | <b>69</b> |

### **Chapitre III : Commande d'un écran VGA par un circuit FPGA**

#### **Cyclone IV**

|                                                                                  |           |

|----------------------------------------------------------------------------------|-----------|

| <b>III.1 Introduction.....</b>                                                   | <b>71</b> |

| <b>III.2 Plateforme de développement QuartusII .....</b>                         | <b>72</b> |

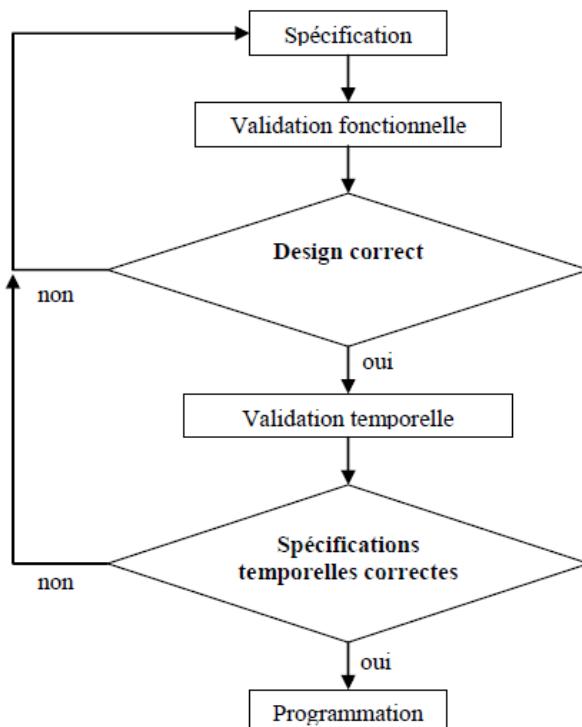

| III.2.1 Déroulement de la conception.....                                        | 72        |

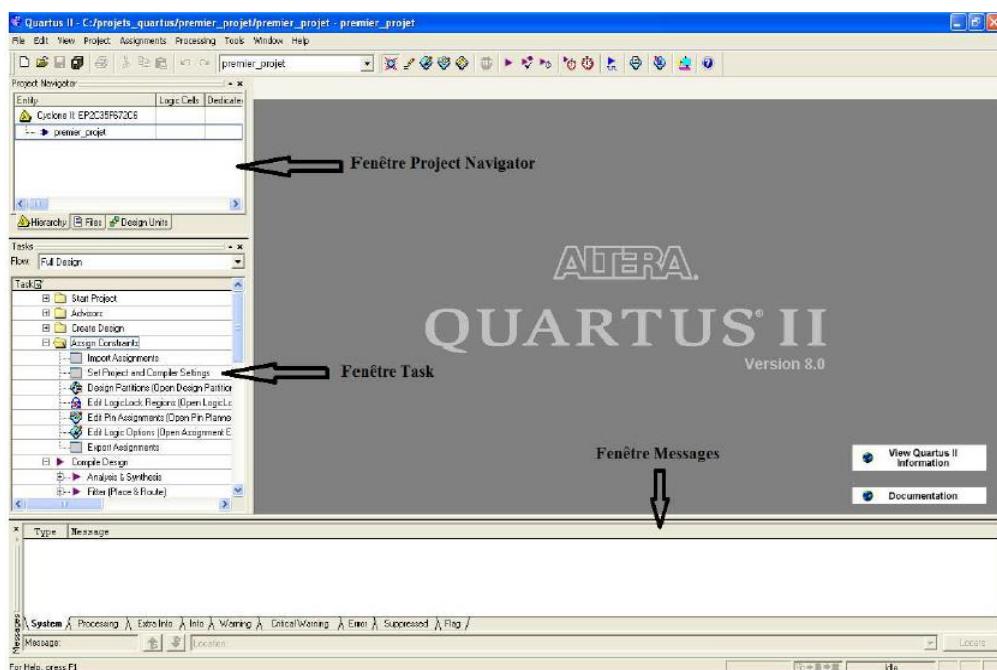

| III.2.2 Présentation .....                                                       | 73        |

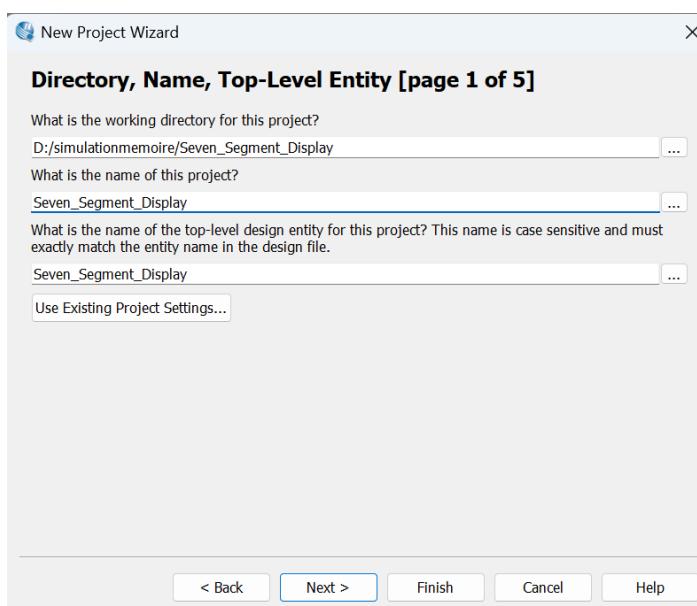

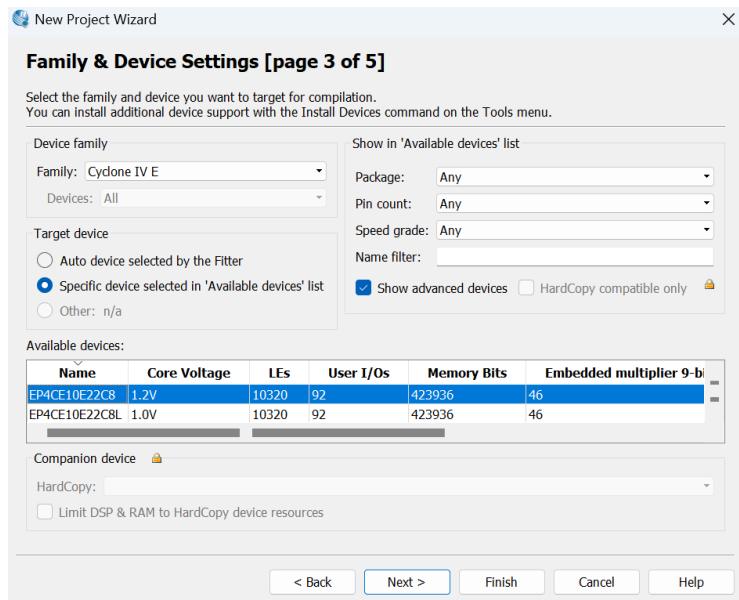

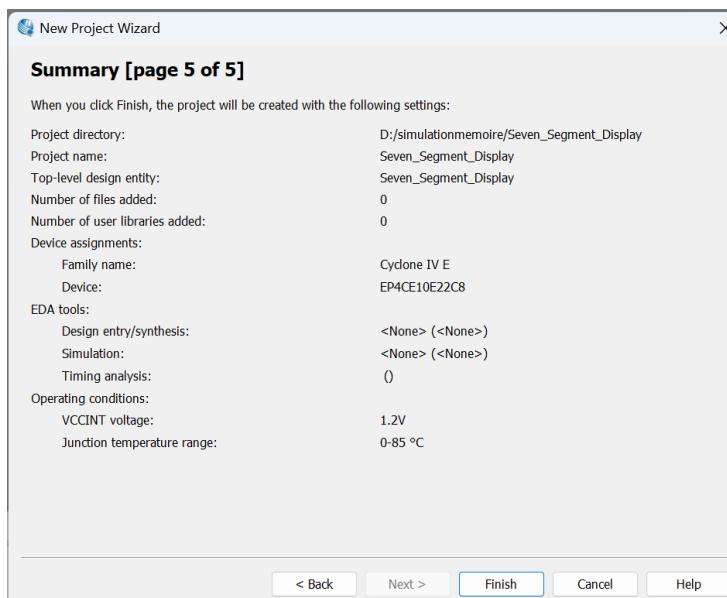

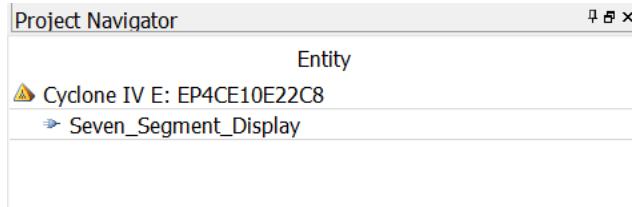

| III.2.3 Création d'un projet.....                                                | 74        |

| III.2.4 Ajout d'une source VHDL.....                                             | 76        |

| III.2.5 Sauvegarde d'un projet .....                                             | 76        |

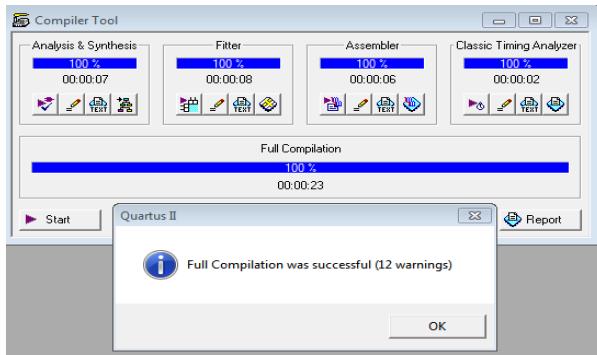

| III.2.6 Compilation .....                                                        | 76        |

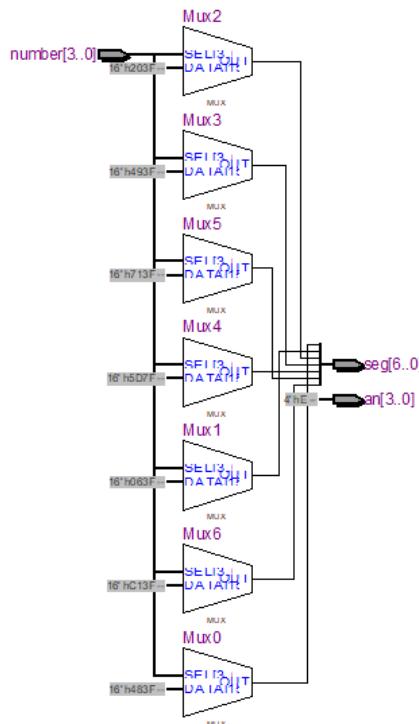

| III.2.7 Schéma fonctionnel (RTL : Register Transfer Level).....                  | 77        |

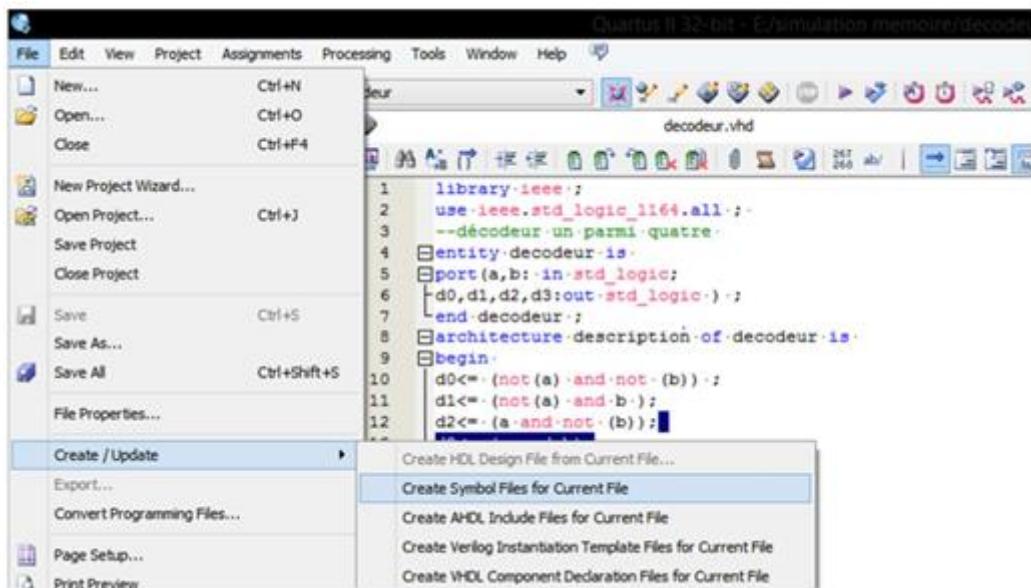

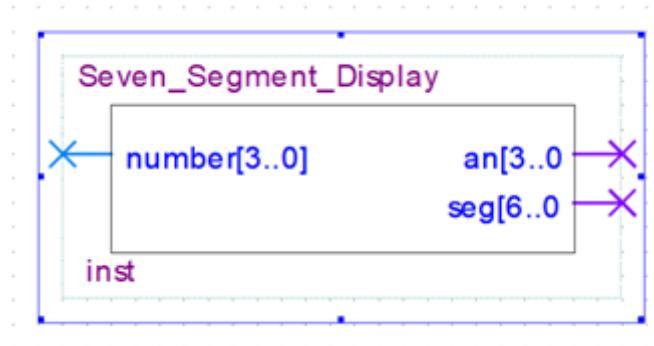

| III.2.8 Création d'un symbole graphique du VHDL.....                             | 78        |

| <b>III.3 Programmation de la maquette Cyclone IV.....</b>                        | <b>78</b> |

| III.3.1 Affectation des pins .....                                               | 79        |

| III.3.2 Etude de Floorplan.....                                                  | 80        |

| III.3.3 Programmation du circuit.....                                            | 80        |

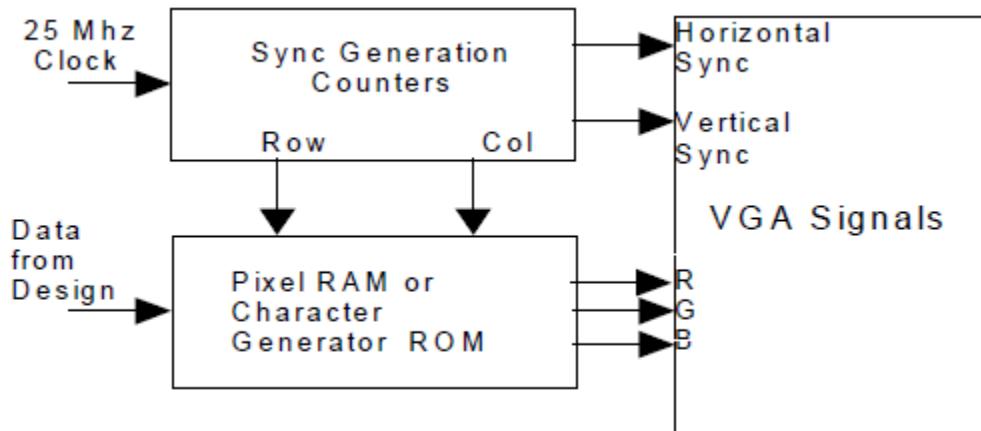

| <b>III.4 Utilisation d'un FPGA pour la génération de signaux vidéo VGA .....</b> | <b>82</b> |

|                                                                                                                                                  |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------|----|

| <b>III.5 Conception vidéo basée sur des caractères : Affichage du message "WELCOME JURY" .....</b>                                               | 83 |

| III.5.1 Description du fonctionnement de ce message .....                                                                                        | 83 |

| III.5.1.1 Déclarations et paramètres VGA.....                                                                                                    | 83 |

| III.5.1.3 ROM de caractères .....                                                                                                                | 85 |

| III.5.1.4 Processus de comptage .....                                                                                                            | 86 |

| III.5.1.5 Génération des signaux de synchronisation.....                                                                                         | 86 |

| III.5.1.6 Génération du signal vidéo .....                                                                                                       | 86 |

| III.5.1.7 Affectation des pins .....                                                                                                             | 86 |

| <b>III.6 Utilisation d'un FPGA/VHDL pour la détection des obstacles et la mesure de la distance en utilisant un capteur ultrasonique.....</b>    | 87 |

| III.6.1 Module de détecteur HC-SR04 .....                                                                                                        | 87 |

| III.6.1.1 Caractéristiques .....                                                                                                                 | 87 |

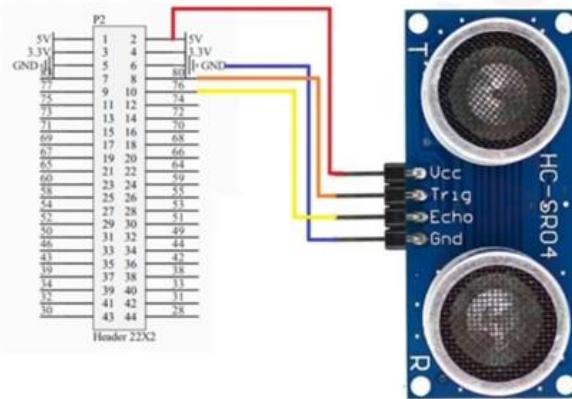

| III.6.1.2 Broches de connexion.....                                                                                                              | 88 |

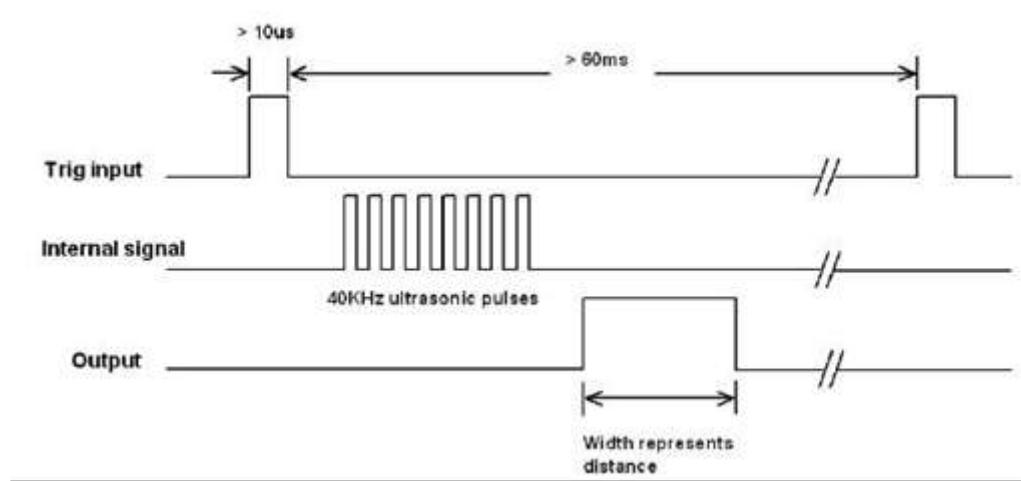

| III.6.1.3 Fonctionnement.....                                                                                                                    | 88 |

| III.6.1.4 Spécifications et limites .....                                                                                                        | 88 |

| III.6.1.5 Communication .....                                                                                                                    | 89 |

| III.6.2 Utilisation du capteur ultrasonique HC-SR04 pour la mesure de la distance et l'affichage sur 7 segments .....                            | 89 |

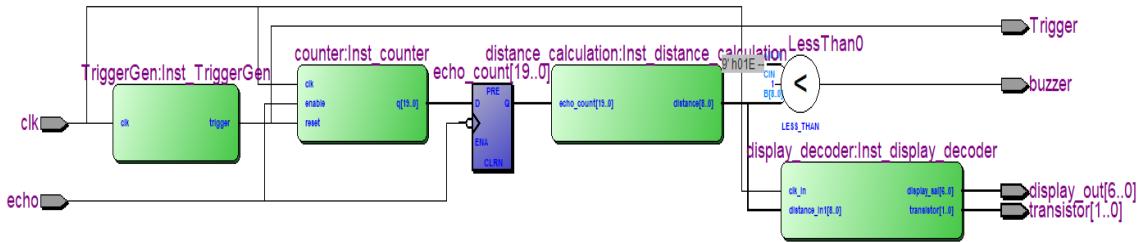

| III.6.2.1 Générateur de Trigger Ultrasonique.....                                                                                                | 90 |

| III.6.2.2 Compteur « counter » .....                                                                                                             | 90 |

| III.6.2.3 Calcul de la Distance .....                                                                                                            | 90 |

| III.6.2.4 L'affichage de la valeur de la distance sur l'afficheur 7 segments .....                                                               | 91 |

| III.6.2.5 Code principal .....                                                                                                                   | 91 |

| III.6.2.6 Affectation des pins .....                                                                                                             | 92 |

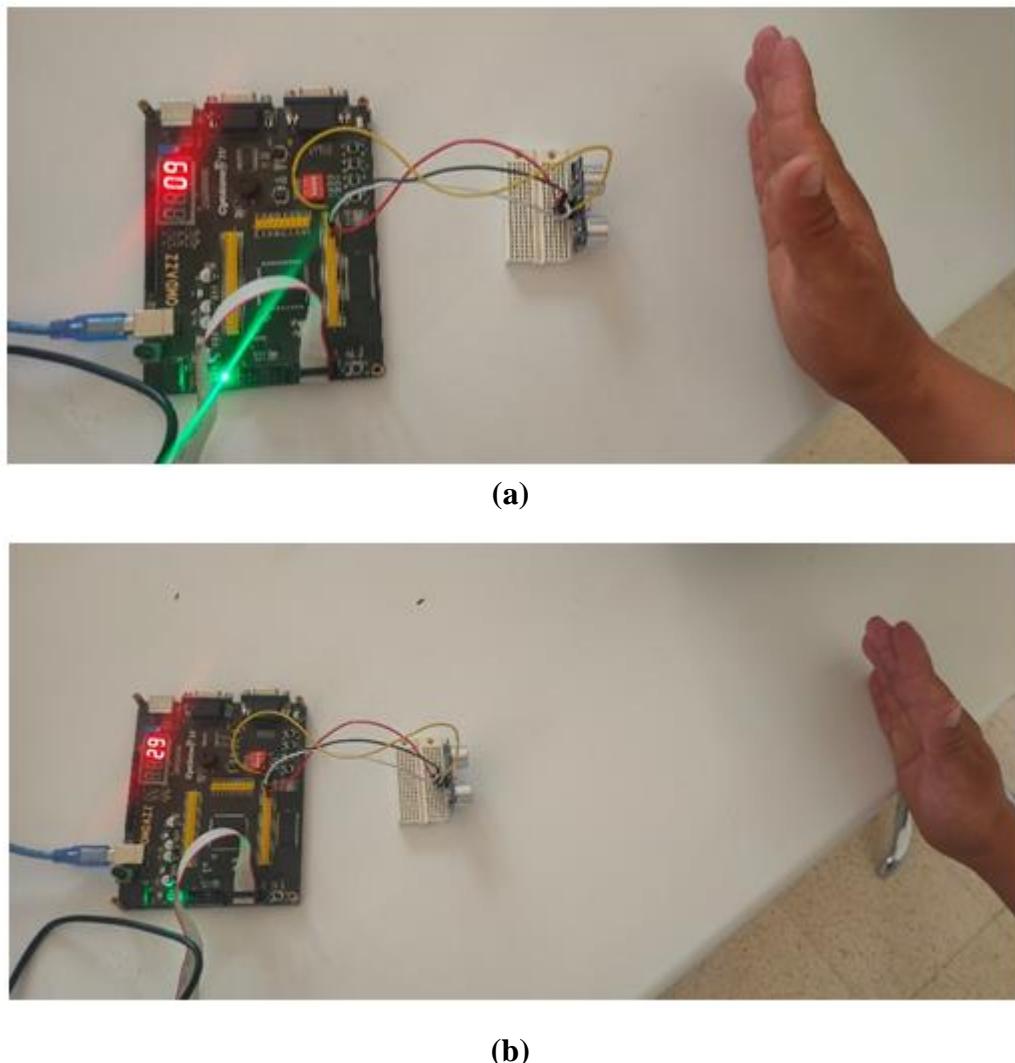

| III.6.2.7 Résultats d'affichage des différentes distances.....                                                                                   | 92 |

| <b>III.7 Utilisation du FPGA cyclone IV pour la génération de signaux vidéo VGA captés par la camera et l'afficher sur un moniteur VGA .....</b> | 93 |

| III.7.1 Connection de la caméra OV7670 et le VGA avec le FPGA .....                                                                              | 93 |

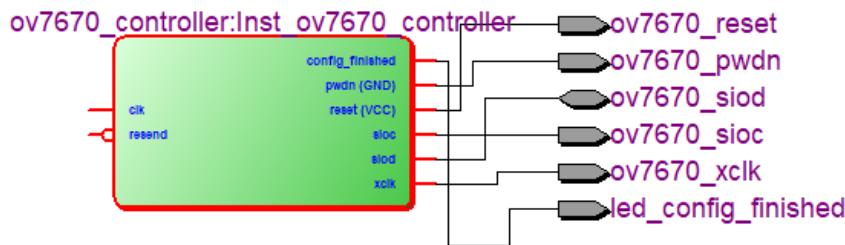

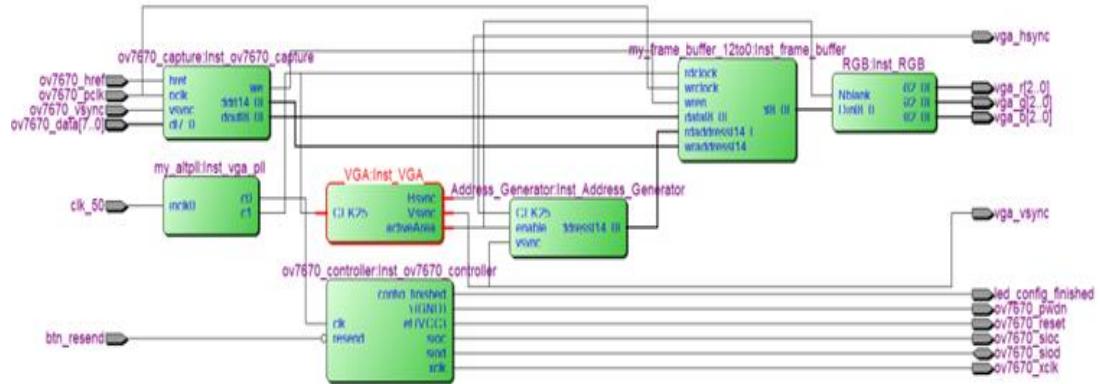

| III.7.1.1 Configuration de la caméra (OV7670_controller.vhd).....                                                                                | 94 |

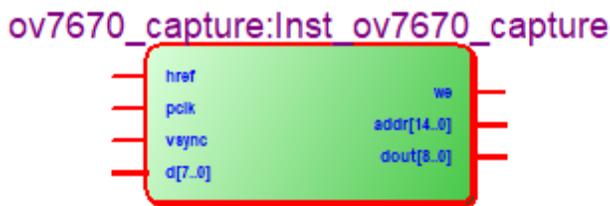

| III.7.1.2 Capture des données d'image (OV7670_capture.vhd) .....                                                                                 | 94 |

|                                                                         |            |

|-------------------------------------------------------------------------|------------|

| III.7.1.3 Sauvegarde des données d'image (frame_buffer.vhd).....        | 95         |

| III.7.1.4 Générateur d'Adresses (Address_Generator.vhd) .....           | 96         |

| III.7.1.5 Module RGB (RGB.vhd) .....                                    | 96         |

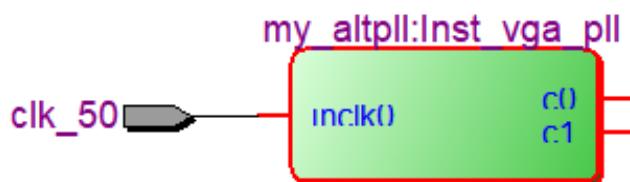

| III.7.1.6 Phase-Locked Loop “PLL” (my_altpll.vhd).....                  | 97         |

| III.7.1.7(VGA.vhd).....                                                 | 97         |

| III.7.1.8 Code principal .....                                          | 98         |

| III.7.1.9 Affectation des pins .....                                    | 98         |

| III.7.1.10 Résultats d'affichage des différentes distances .....        | 99         |

| III.7.1.10.1 Conception matérielle .....                                | 99         |

| III.7.1.10.2 Mémoire vidéo VGA .....                                    | 100        |

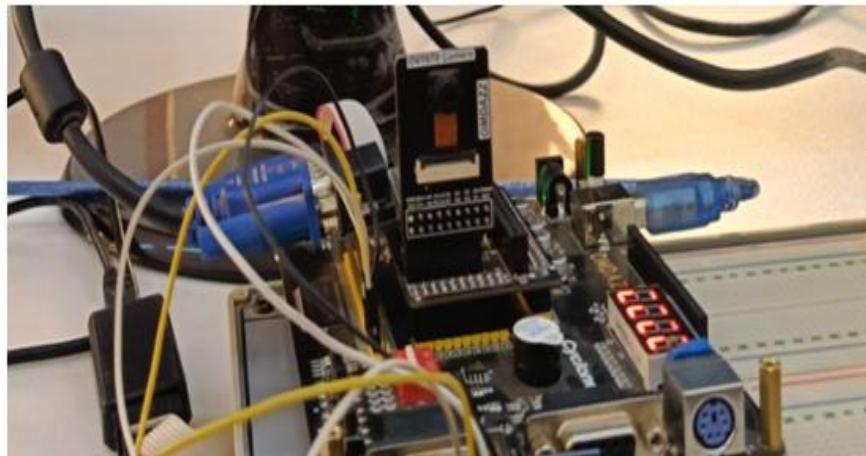

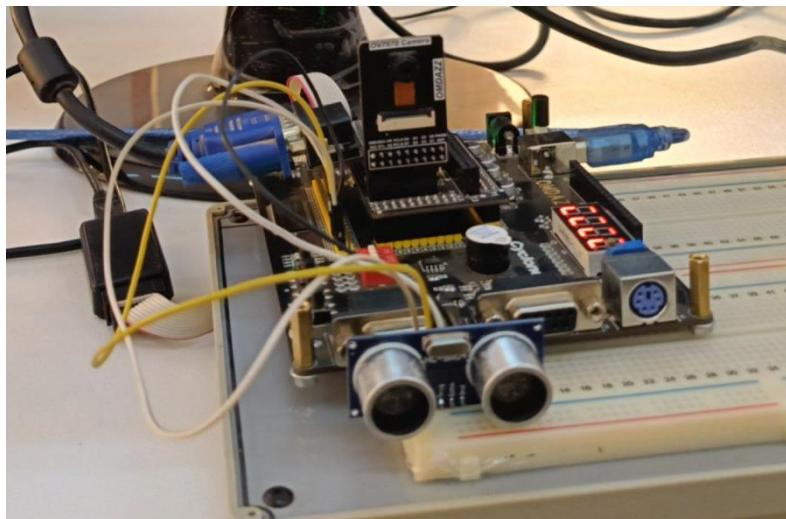

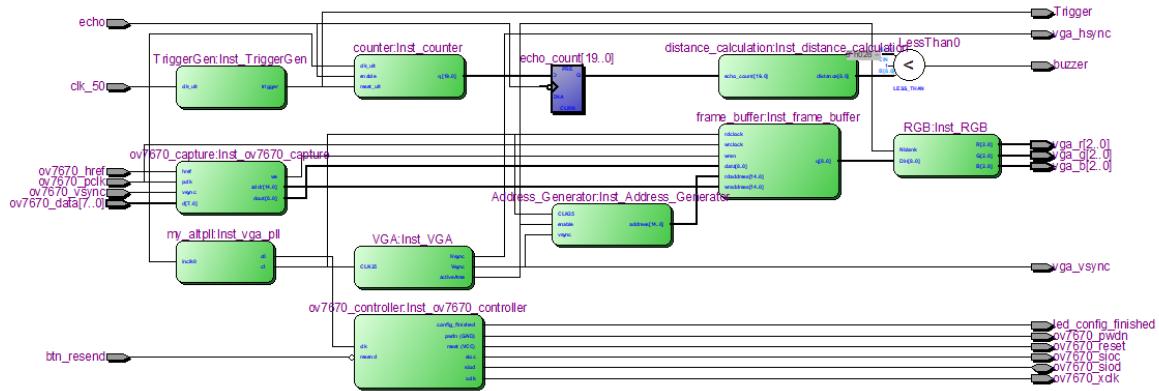

| III.7.2 Intégration de la Caméra OV7670 et du Capteur Ultrasonique..... | 101        |

| III.7.2.1 Affectation des pins .....                                    | 102        |

| <b>III.8 Conclusion .....</b>                                           | <b>103</b> |

| <b>Références Bibliographiques Chapitre III.....</b>                    | <b>104</b> |

| <b>Conclusion Générale .....</b>                                        | <b>105</b> |

## LISTE DES FIGURES

|                                                                                                                           |    |

|---------------------------------------------------------------------------------------------------------------------------|----|

| <b>Figure I.1:</b> Architecture conceptuelle d'un FPGA (Architecture, Interconnexions et CLB). .....                      | 6  |

| <b>Figure I.2:</b> Architecture interne des FPGAs .....                                                                   | 7  |

| <b>Figure I.3:</b> Différents secteurs d'un FPGA .....                                                                    | 7  |

| <b>Figure I.4:</b> Exemple de blocs logiques de différents fabricants .....                                               | 8  |

| <b>Figure I.5:</b> Structure générale du routage .....                                                                    | 9  |

| <b>Figure I.6:</b> Symbole de Cyclone IV d'Altera. ....                                                                   | 10 |

| <b>Figure I.7:</b> Caractéristiques architecturales clés du FPGA Cyclone IV.....                                          | 11 |

| <b>Figure I.8:</b> Structure d'un Logic Element .....                                                                     | 12 |

| <b>Figure I.9:</b> Connexions chaînées entre LEs dans un LAB de circuit Cyclone IV ...                                    | 14 |

| <b>Figure I.10:</b> Structure LAB de circuit Cyclone IV .....                                                             | 14 |

| <b>Figure I.11:</b> Puissance Cyclone IV E (à gauche) et Cyclone IV GX (à droite) .....                                   | 17 |

| <b>Figure I.12:</b> Programmation d'un périphérique de configuration série avec une solution de chargeur flash série..... | 18 |

| <b>Figure I.13:</b> Critères de choix du circuit logique programmable FPGA.....                                           | 20 |

| <b>Figure I.14:</b> Statistiques du marché occupé par les vendeurs d'FPGA.....                                            | 21 |

| <b>Figure I.15:</b> Reprogrammabilité sur site d'un FPGA.....                                                             | 21 |

| <b>Figure I.16:</b> Mode d'exécution matériel des outils de CAO. ....                                                     | 22 |

| <b>Figure I.17:</b> Cycle de programmation d'un FPGA en utilisant les outils de CAO. .                                    | 24 |

| <b>Figure I.18:</b> Carte de développement FPGA Altera Cyclone IV EP4CE10E22C8.25                                         |    |

| <b>Figure I.19:</b> Constitution de la carte de développement FPGA Altéra Cyclone IV.                                     |    |

| .....                                                                                                                     | 27 |

| <br>                                                                                                                      |    |

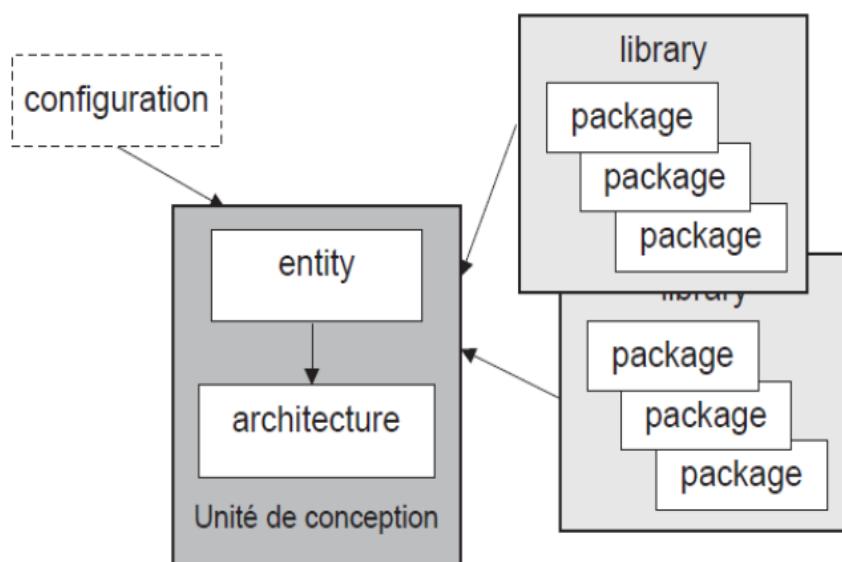

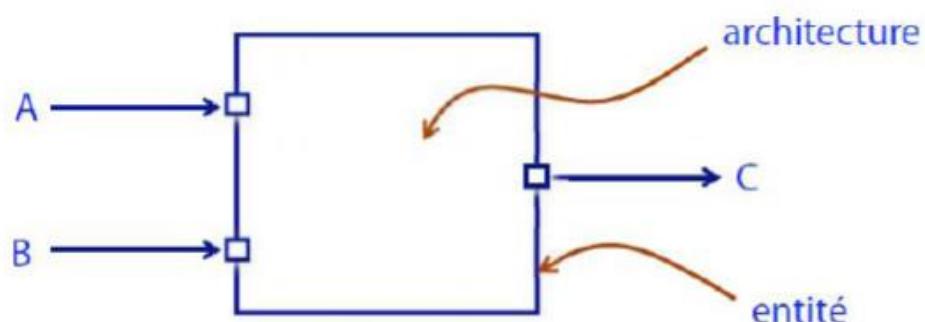

| <b>Figure II.1:</b> Représentation d'une unité de conception.....                                                         | 33 |

| <b>Figure II.2:</b> Représentation d'une unité de conception.....                                                         | 36 |

| <b>Figure II.3:</b> Représentation d'une unité de conception.....                                                         | 37 |

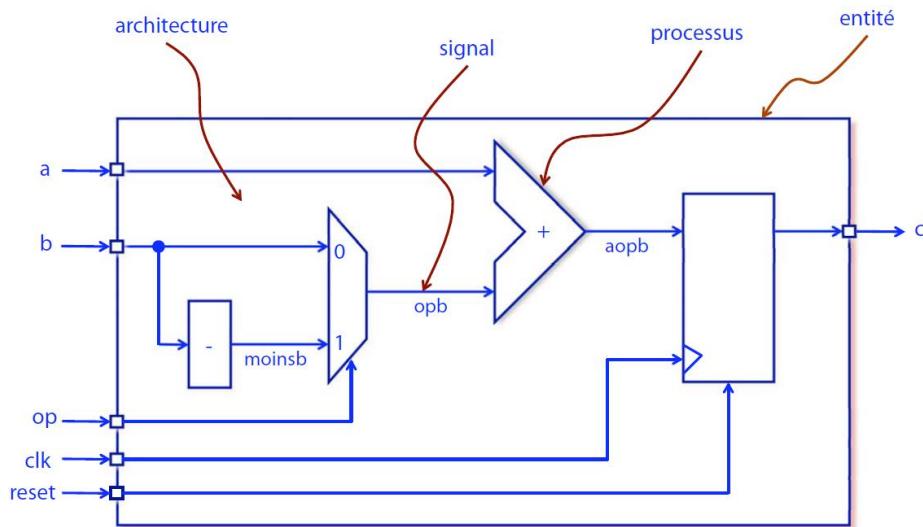

| <b>Figure II.4:</b> Représentation d'une unité de conception.....                                                         | 41 |

| <b>Figure II.5:</b> Représentation d'une unité de conception.....                                                         | 42 |

| <b>Figure II.6:</b> Instructions en mode séquentiel. ....                                                                 | 44 |

| <b>Figure II.7:</b> Différentes étapes de l'implémentation sur FPGA. ....                                                 | 52 |

| <b>Figure II.8:</b> Elément d'une image (le pixel).....                                                                   | 53 |

|                                                                                                                |    |

|----------------------------------------------------------------------------------------------------------------|----|

| <b>Figure II.9:</b> Composition additive des couleurs .....                                                    | 55 |

| <b>Figure II.10:</b> Présentation des couleurs dans l'espace RGB.....                                          | 55 |

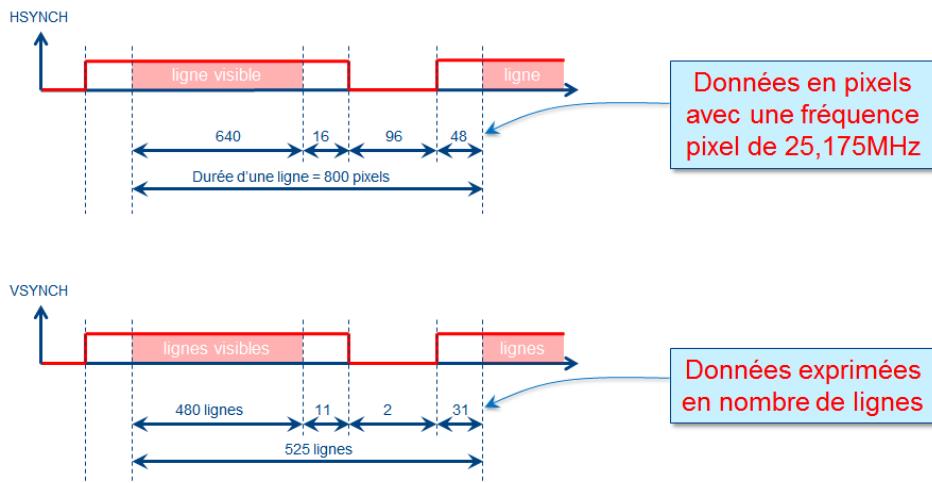

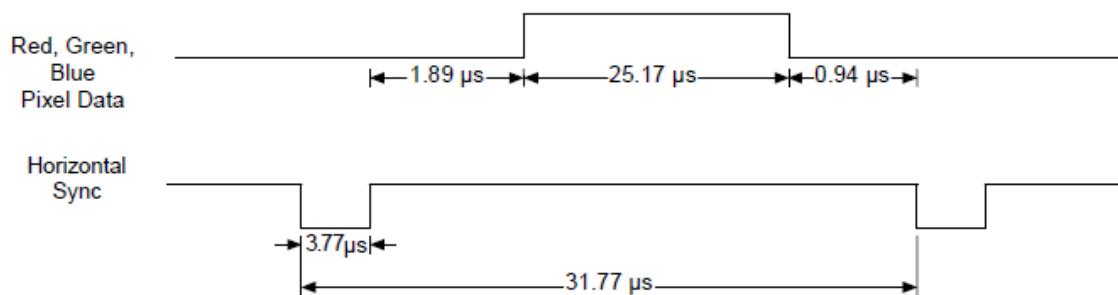

| <b>Figure II.11:</b> Signaux de synchronisation de l'affichage VGA. ....                                       | 57 |

| <b>Figure II.12:</b> Signaux de synchronisation horizontale et verticale de l'affichage<br>VGA.....            | 57 |

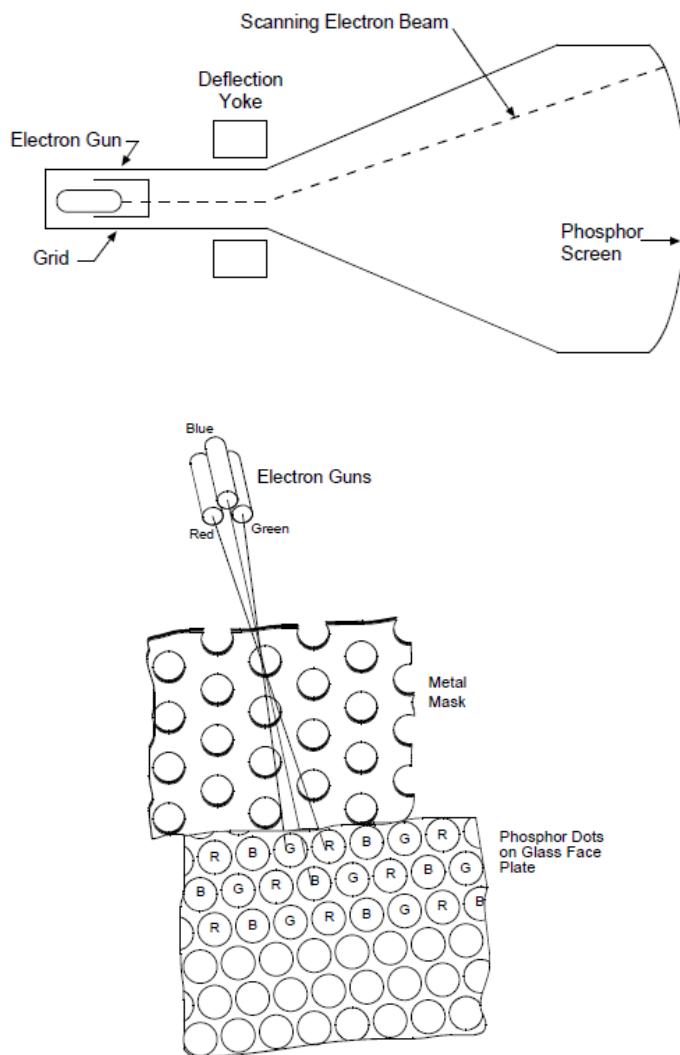

| <b>Figure II.13:</b> CRT (Cathode Ray Tube) couleur et points phosphoreux sur la face<br>de l'écran. ....      | 59 |

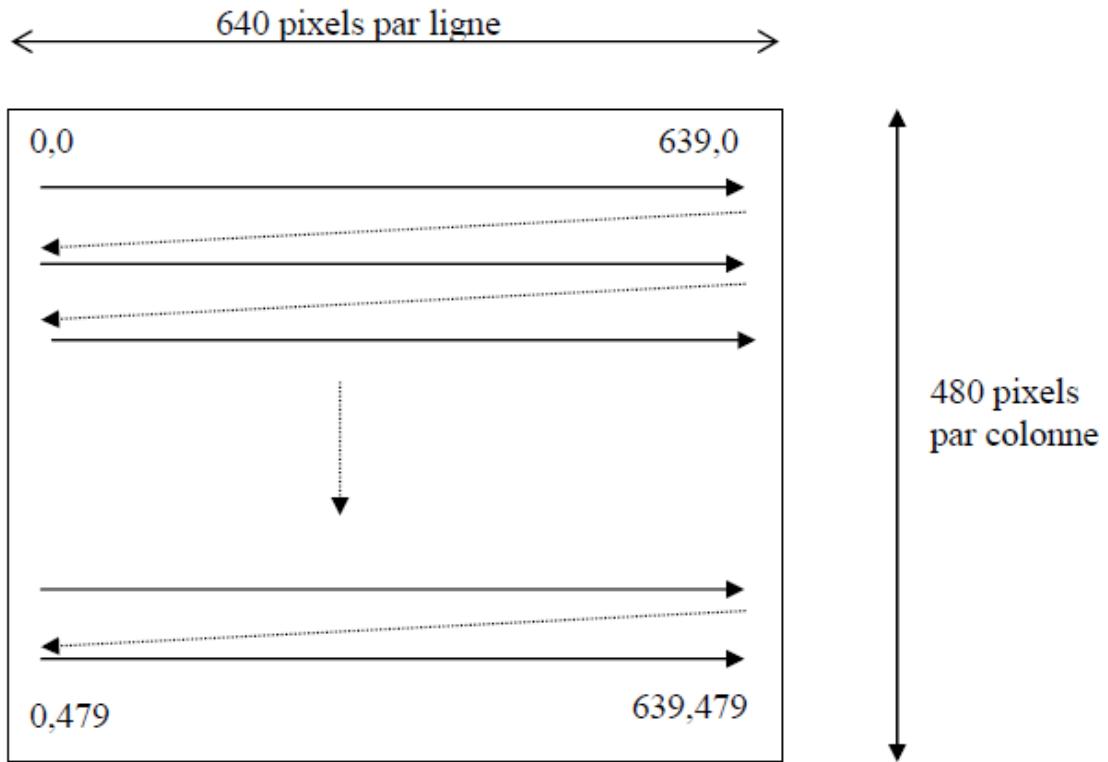

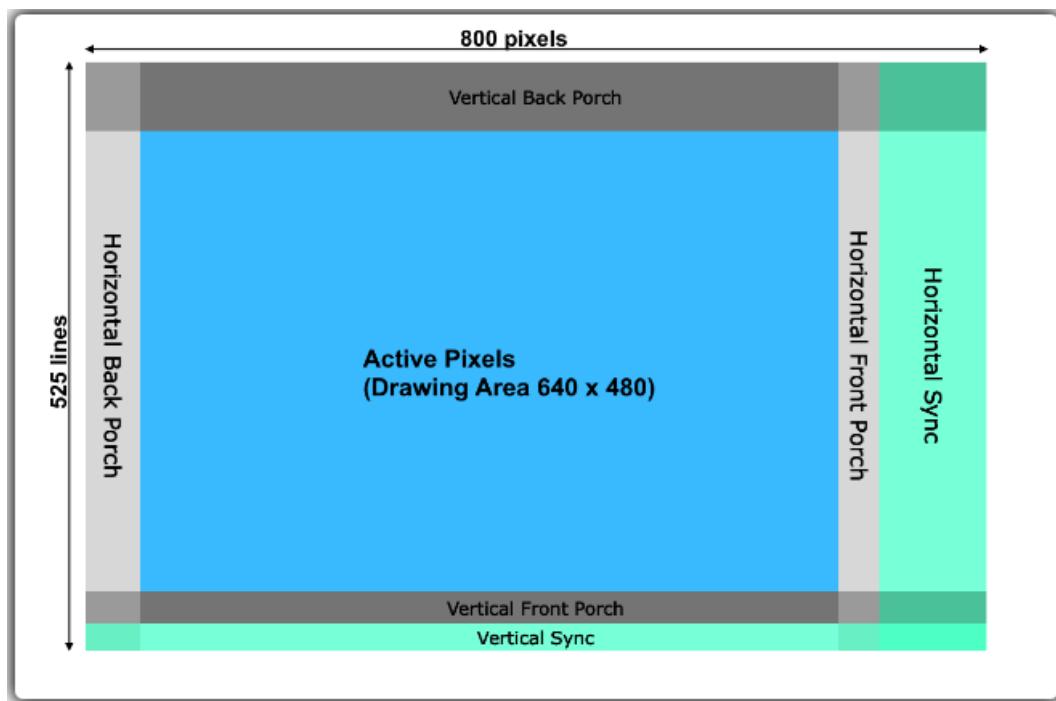

| <b>Figure II.14:</b> Image VGA - Disposition 640 par 480 pixels. ....                                          | 60 |

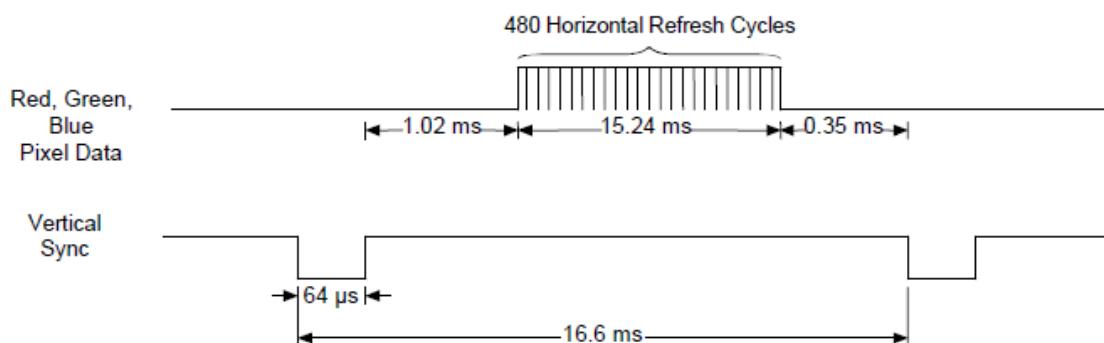

| <b>Figure II.15:</b> Signal de synchronisation verticale de l'affichage VGA pour 640 par<br>480 à 60 Hz. ....  | 61 |

| <b>Figure II.16:</b> Signal de synchronisation horizontale de l'affichage VGA pour 640<br>par 480 à 60 Hz..... | 61 |

| <b>Figure II.17:</b> Fonctionnement d'un système de vision .....                                               | 63 |

| <b>Figure II.18:</b> Carte FPGA avec les modules OV7670 et VGA. ....                                           | 64 |

| <b>Figure II.19:</b> La carte FPGA avec les modules .....                                                      | 64 |

| <b>Figure II.20:</b> Connecteur VGA. ....                                                                      | 65 |

| <b>Figure II.21:</b> Connectique VGA d'une FPGA Cyclone IV.....                                                | 65 |

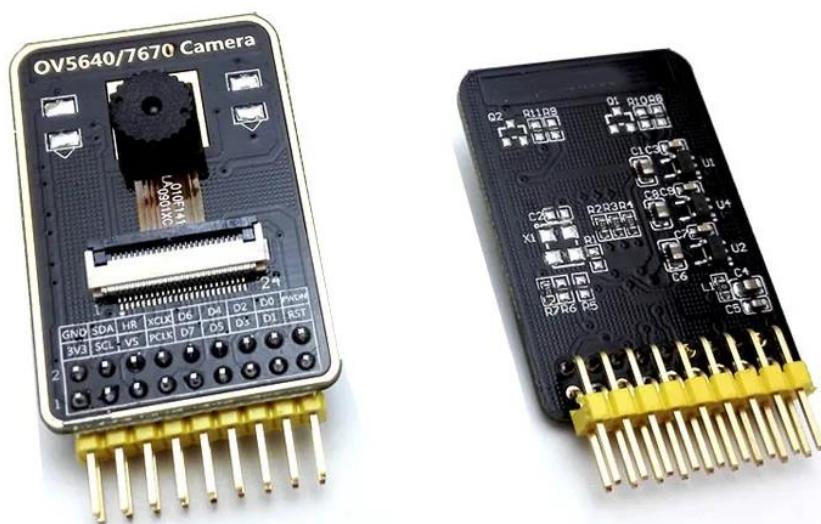

| <b>Figure II.22:</b> Caméra OV7670 utilisé dans notre réalisation pratique.....                                | 66 |

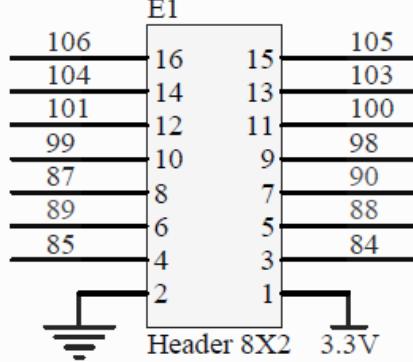

| <b>Figure II.23:</b> Schéma de la caméra et comment la connecter au FPGA .....                                 | 67 |

| <br>                                                                                                           |    |

| <b>Figure III.1:</b> Déroulement de la conception. ....                                                        | 72 |

| <b>Figure III.2:</b> Environnement de développement Quartus II.....                                            | 73 |

| <b>Figure III.3:</b> Création d'un projet sous quartus II.....                                                 | 74 |

| <b>Figure III.4:</b> Fenêtre de choix du circuit. ....                                                         | 75 |

| <b>Figure III.5:</b> Fenêtre de création du projet finie. ....                                                 | 76 |

| <b>Figure III.6:</b> Fenêtre de type de projet. ....                                                           | 76 |

| <b>Figure III.7:</b> Fenêtre de Seven_Segment_Display.vhdl.....                                                | 76 |

| <b>Figure III.8:</b> Fenêtre de compilation projet « Seven_Segment_Display ». ....                             | 77 |

| <b>Figure III.9:</b> Schéma fonctionnel RTL de Seven_Segment_Display.....                                      | 77 |

| <b>Figure III.10:</b> Schéma fonctionnel RTL de Seven_Segment_Display.....                                     | 78 |

| <b>Figure III.11:</b> Symbole graphique de Seven_Segment_Display.....                                          | 78 |

| <b>Figure III.12:</b> Fenêtre de type d'assignement des pins.....                                              | 79 |

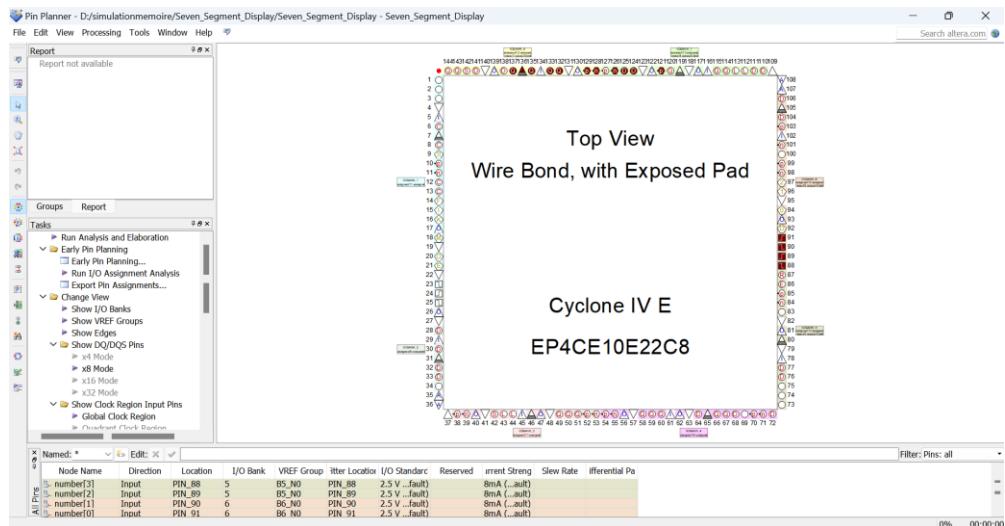

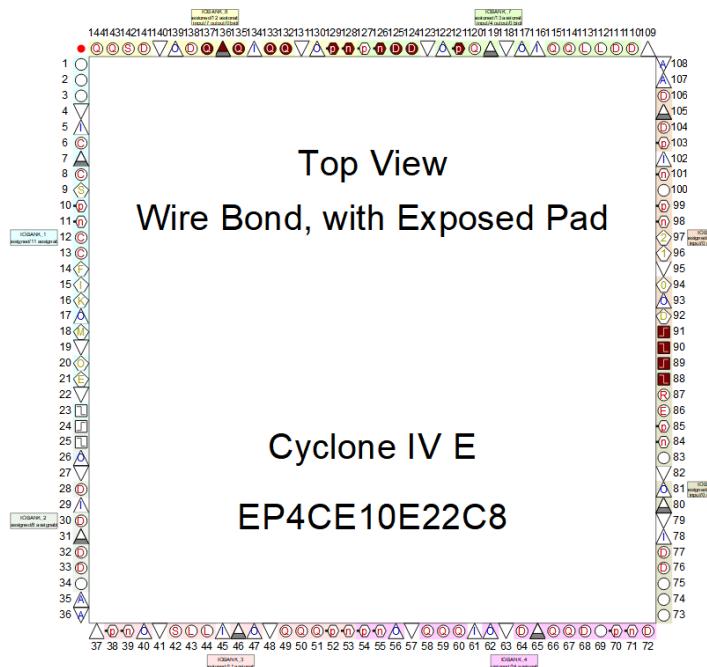

| <b>Figure III.13:</b> Plan de cablage du FPGA.....                                                             | 80 |

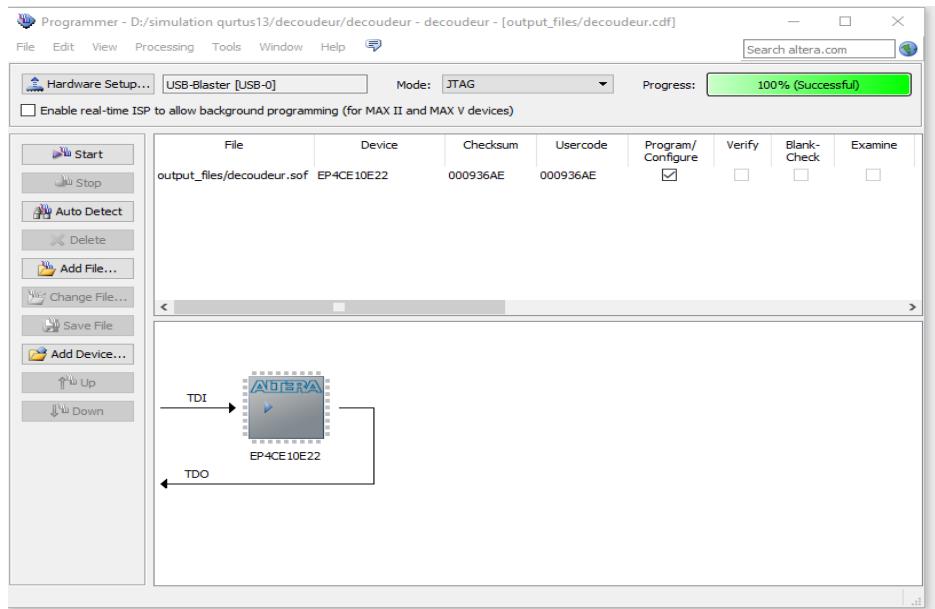

| <b>Figure III.14:</b> Boite de dialogue de programmation.....                                                  | 81 |

| <b>Figure III.15:</b> Plateforme Cyclone IV programmée. ....                                                   | 81 |

| <b>Figure III.16:</b> Génération FPGA de signaux vidéo VGA. ....                                               | 82 |

| <b>Figure III.17:</b> Protocole de synchronisation.....                                                        | 84 |

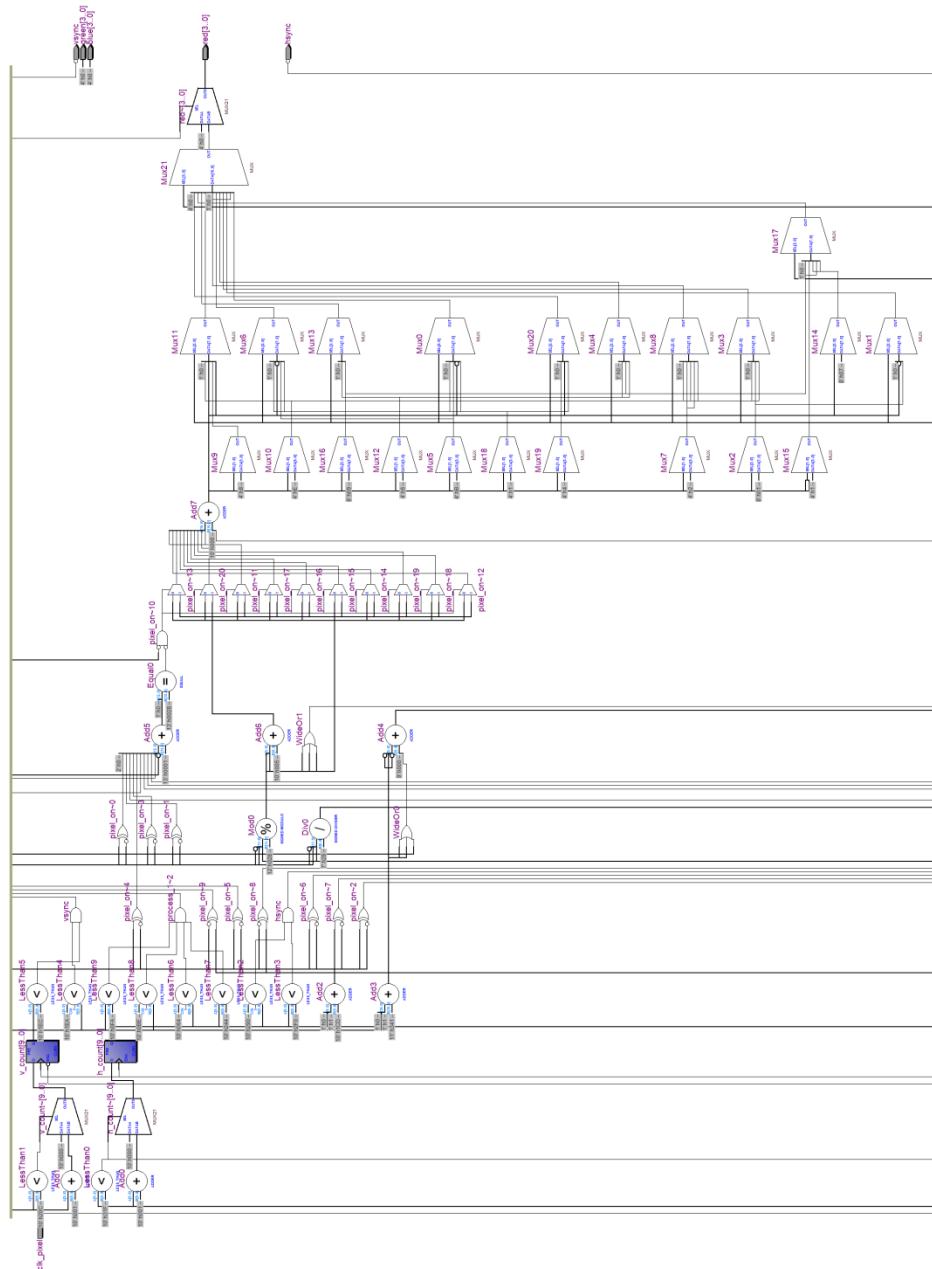

| <b>Figure III.18:</b> Schéma fonctionnel RTL de message WELCOME JURY.....                                      | 85 |

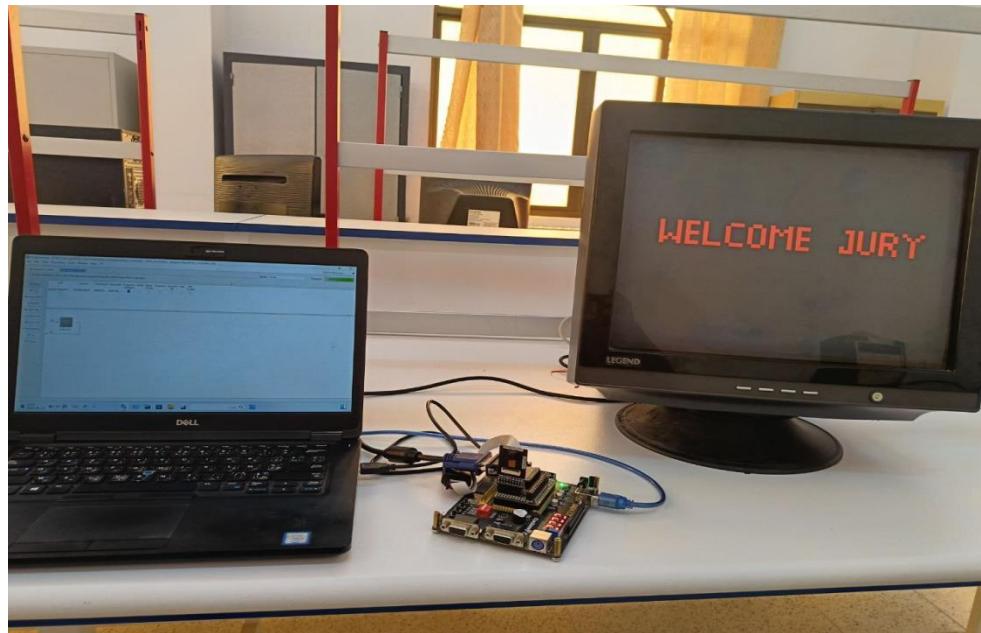

| <b>Figure III.19 :</b> Affichage de message WELCOME JURY sur l'écran VGA.....                                  | 87 |

| <b>Figure III.20:</b> Capteur ultrason HC-SR04.....                                                            | 87 |

|                                                                                                                           |     |

|---------------------------------------------------------------------------------------------------------------------------|-----|

| <b>Figure III.21:</b> Diagramme de fonctionnement du capteur ultrason.....                                                | 88  |

| <b>Figure III.22:</b> Connexion entre notre FPGA et HC-SR 04. ....                                                        | 89  |

| <b>Figure III.23:</b> Schéma fonctionnel RTL principal de programme VHDL « ultrasonic».....                               | 92  |

| <b>Figure III.24:</b> Des exemples de la distance mesurée: (a) 09 cm, (b) 29 cm. ....                                     | 93  |

| <b>Figure III.25:</b> Schéma principal pour connecter la caméra OV7670 et VGA avec FPGA. ....                             | 94  |

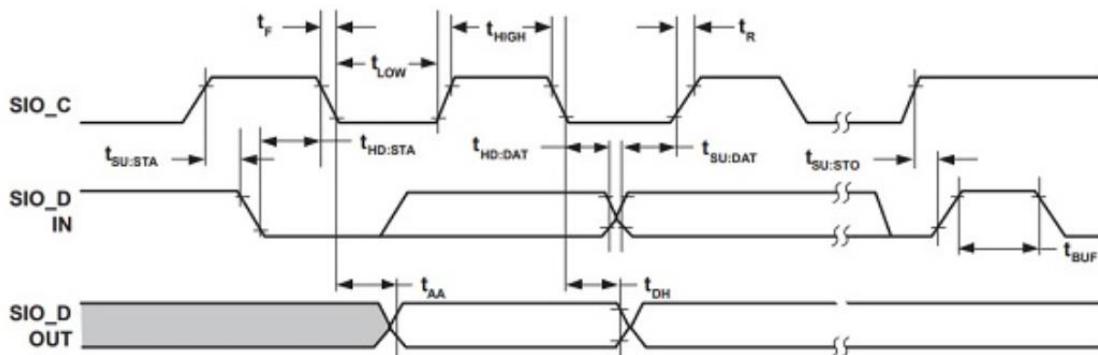

| <b>Figure III.26 :</b> Interface SCCB de type I2C pour communiquer avec la caméra OV7670.....                             | 94  |

| <b>Figure III.27:</b> Schéma RTL du programme VHDL « OV7670_controller».....                                              | 95  |

| <b>Figure III.28:</b> RTL du programme VHDL « OV7670_capture».....                                                        | 95  |

| <b>Figure III.29:</b> RTL du programme VHDL « frame_buffer».....                                                          | 96  |

| <b>Figure III.30:</b> RTL du programme VHDL « Address_Generator».....                                                     | 96  |

| <b>Figure III.31:</b> RTL du programme VHDL « RGB».....                                                                   | 97  |

| <b>Figure III.32:</b> RTL du programme VHDL « my_altpll».....                                                             | 97  |

| <b>Figure III.33:</b> RTL du programme VHDL « VGA».....                                                                   | 98  |

| <b>Figure III.34:</b> Schéma fonctionnel RTL de code principal « camera.vhd » .....                                       | 99  |

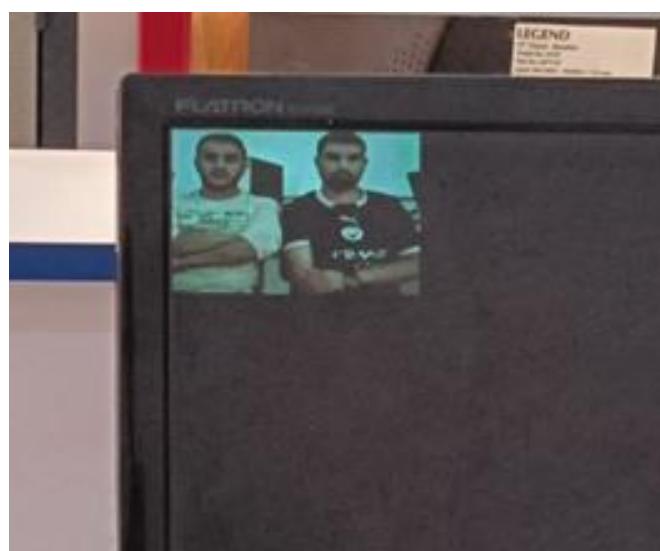

| <b>Figure III.35:</b> L'image des étudiants affichée sur le moniteur VGA de taille 160x120 pixels. ....                   | 100 |

| <b>Figure III.36:</b> Flux d'image en direct de la caméra CMOS OV7670 diffusé sur l'écran VGA.....                        | 100 |

| <b>Figure III.37:</b> Schéma principal pour connecter la caméra OV7670, VGA et le capteur ultrasonique avec le FPGA. .... | 101 |

| <b>Figure III.38:</b> Schéma fonctionnel RTL du code principal de la camera intégrée avec le capteur ultrasonique .....   | 102 |

## LISTE DES TABLEAUX

|                                                                                                                                                                                               |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| <b>Tableau II.1:</b> Ecriture des opérateurs logique en VHDL.....                                                                                                                             | 46  |

| <b>Tableau II.2:</b> Ecriture des opérateurs relationnels en VHDL.....                                                                                                                        | 47  |

| <b>Tableau II.3:</b> Brochage de la caméra OV7670.....                                                                                                                                        | 67  |

| <b>Tableau III.1:</b> Numéros des pins entrées/sorties .....                                                                                                                                  | 79  |

| <b>Tableau III.2:</b> Numéros des pins entrées/sorties utilisés de l'affichage du message<br>WELCOME JURY .....                                                                               | 86  |

| <b>Tableau III.3:</b> Spécifications et limites du capteur ultrason .....                                                                                                                     | 89  |

| <b>Tableau III.4 :</b> Tableau III. 4: Numéros des pins entrées/sorties utilisés par le<br>capteur ultrasonique Numéros des pins entrées/sorties utilisés par le capteur<br>ultrasonique..... | 92  |

| <b>Tableau III.5:</b> Numéros des pins entrées/sorties utilisés pour les différents<br>composants du système.....                                                                             | 99  |

| <b>Tableau III.6:</b> Numéros des pins entrées/sorties utilisés dans le cas d'intégration de<br>la caméra avec l'ultrasonique.....                                                            | 102 |

## LISTE DES ABREVIATIONS

### A

**ASM:** Algorithmic Sequential Machines

**ASIC:** Application Specific Integrated Circuit.

### C

**CAO:** Conception Assistée par Ordinateur.

**CLB:** Configurable Logic Block.

**CPLD :** Complex Programmable Logic Device.

**CMOS:** Complementary Metal–Oxide–Semiconductor.

### D

**DC** : Direct Current.

**DSP:** Digital Signal Processor.

**DoD:** Department of Defense (United States).

### F

**FPGA:** Field Programmable Gate Arrays.

**FIFO :** First In, First Out

### H

**HDL :** Hardware Description Language (langage de description matériel).

**HSYNCH :** Synchronisation Horizontale

### I

**IEEE:** Institut of Electrical and Electronics Engineers.

**IOB:** Input Output Bloc.

**IEO:** Element D'entrée/Sortie

### J

**JTAG:** Joint Test Action Group

### L

## Liste des abréviations

---

**LAB:** Logic Array Bloc.

**LE :** Elément Logique.

**LSI :** Large Scale Integration.

**LUT :** Look up Table.

**LCD :** Liquid Crystal Display

**LED :** Diode Electroluminescente

**LC :** Cellule Logique

### P

---

**PAL:** Programmable Array Logic

**PLD:** Programmable Logic Device

**PLL :** Phase-Locked Loop

### M

---

**MIF :** Memory Initialization File

### R

---

**RAM:** Random Access Memoy.

**ROM:** Read-Only Memory

**RGB :** Rouge Vert Bleu

**RTL:** Register Transfer Level.

### S

---

**SRAM:** Static Random Access Memory.

### T

---

**TTL :** Transistor-Transistor Logic

### V

---

**VHDL:** VHSIC Hardware Description Language.

**VHSIC:** Very High Speed Integrated Circuit.

**VGA :** Video Graphics Adapter

**VLSI:** Very Large Scale Integration.

# *INTRODUCTION GÉNÉRALE*

## **INTRODUCTION GENERALE**

Depuis la commercialisation du premier circuit programmable FPGA en 1985, l'utilisation de ces circuits ne cesse de s'étendre à des domaines et applications variés, parmi lesquels nous pouvons citer le traitement d'image et de vidéos [1], [2], les réseaux de neurones [3], la comparaison de séquences génétiques [4], l'architecture des ordinateurs [5] etc... L'intérêt suscité par les FPGA est dû essentiellement à leurs prix abordables, facilité de mise en œuvre et flexibilité [6].

Dans notre vie quotidienne, l'image joue un rôle de plus en plus important pour nous informer ou nous divertir. En parallèle, le traitement de l'information s'est lui aussi développé grâce à l'évolution de la microélectronique en proposant des systèmes de plus en plus performants pour exécuter des algorithmes très complexes. Les progrès dans la capacité d'intégration des circuits électroniques ont ouvert de nouvelles perspectives pour le traitement d'images en temps réel sur des systèmes embarqués. D'un côté, des processeurs spécifiques peuvent couramment effectuer des milliards d'opérations par seconde et d'un autre côté, des composants reprogrammables comporteront dans un avenir proche plusieurs milliards de portes logiques. Ces circuits permettent de réaliser des applications avec des performances en termes de vitesse de traitement sans cesse croissantes

Pour réaliser une application avec un FPGA il faut décrire le circuit électronique à réaliser avec un langage de description matérielle comme le VHDL. Puis il faut synthétiser cette description en circuit électronique. Cette étape et les suivantes peuvent se faire avec des logiciels gratuits fournies par le fabricant de circuit. Enfin après une étape de placement et routage qui prend en compte l'architecture du FPGA, un fichier de configuration appelé bitstream est généré. Celui-ci permet de spécifier au FPGA lors de la configuration la position des points de la mémoire de configuration.

L'étude que nous présentons dans ce mémoire vise la conception, la génération et l'implémentation des descriptions textuelles (VHDL) sur un FPGA de la famille Cyclone IV de type EP4CE10E22C8 dont les sorties sont directement reliées à un connecteur pour écran VGA par le logiciel Quartus II afin de générer des images et des caractères sur un écran vidéo VGA.

L'écran du moniteur pour un format VGA standard contient 640 colonnes par 480 lignes d'éléments d'image appelé pixel. Une image est affichée sur l'écran en allumant et en éteignant individuellement les pixels. La combinaison de nombreux pixels génère une image.

L'objectif de notre travail est de construire une plate-forme d'imagerie FPGA en utilisant un langage de description matériel le VHDL. Le principe est d'interfacer une caméra CMOS de résolution VGA avec la carte de développement OMDAZZ et de transmettre le flux vidéo en direct acquis sur un moniteur VGA. Les images de la caméra sont diffusées sur un moniteur VGA à 30 images par seconde. Nos images sont affichées sur 160x120 pixels puisque le FPGA cyclone IV quand on a utilisé n'a pas assez de mémoire pour stocker l'image VGA complète.

Ce mémoire se divise en trois chapitres organisés de la manière qui suit:

Dans le premier chapitre nous nous intéressons aux circuits logiques programmables et en particulier les FPGA et la présentation de notre carte FPGA.

Le deuxième chapitre, traite l'outil indispensable pour la programmation d'un FPGA qui est le langage VHDL et les fonctionnalités de base de celui-ci lors des phases de conception ou de synthèse, ensuite nous donnons une généralité sur l'image, le signal vidéo VGA et comment générer l'affichage vidéo VGA à l'aide d'un FPGA, une présentation de la vision artificielle et le montage de la caméra et le module VGA avec la carte FPGA Cyclone IV.

Le troisième chapitre a débuté par une description détaillée sur la méthode de conception et d'implémentation des circuits dans un FPGA on utilisant le logiciel Quartus II, en finira par la présentation de nos programmes VHDL (les schémas

fonctionnels RTL) et les résultats de génération de l'affichage des écrans vidéo des caractères et des images captées par une caméra CMOS OV7670.

Dans un premier temps, nous allons afficher le message "WELCOME JURY" sur l'écran pour l'accueil. Ensuite, nous avons utilisé un capteur ultrasonique pour mesurer la distance et afficher la valeur mesurée sur un afficheur à sept segments. Lorsque quelqu'un entre dans une zone de 30 cm, un buzzer s'active pour alerter de sa présence.

Ensuite, nous allons intégrer une caméra pour capturer une vidéo en temps réel et l'afficher sur un écran VGA avec une résolution de 160x120. Enfin, nous avons combiné les fonctionnalités de la caméra et du capteur ultrasonique pour activer le buzzer lorsqu'une personne entre dans le champ de détection, sans afficher la distance mesurée sur l'afficheur à sept segments.

Enfin, nous terminons notre travail avec une conclusion générale dressera le bilan de cette étude.

## **REFERENCES BIBLIOGRAPHIQUES -INTRODUCTION-**

- [1] **S. C. Chan, H.O. Ngai and K.L. Ho**, "A programmable image processing system using FPGA" International journal of electronics, vol 75, N°4 pp 725-730, 1993.

- [2] **M. Alves de barros**, "Traitement bas niveau d'images en temps réel et circuits reconfigurables" Thèse de doctorat, Université de Paris-Sud, 1994.

- [3] **J.G. Eldrerge, B.L. Hutchings**, "Density enhancement of neural network using FPGAs and run-time reconfiguration" FCCM, 1994.

- [4] **E. Lemoine, J. Quinqueton and J. Salantin**, "High speed pattern matching in genetic data base with reconfigurable hardware" Proceeding of th 2nd INT. Conf. o, Intelligent systems for molecular biology, pp 269-276. AAAI, 1994.

- [5] **B.Heeb and C. Pfister**, "Chameleon, a workstation of a different colour" 2nd International Workshop on Field-Programmable Logic Applications, paper 5.6, Vienna, Austria, 1992.

- [6] **H.Guermoud, Y.Berviller, E.Tisserand, S.Weber**, « Architecture à base de FPGA dynamiquement dédiée au traitement d'image sur flot de données », SEIZIÈME COLLOQUE GRETSI — 15-19 SEPTEMBRE 1997 — GRENOBLE

# *Chapitre I*

## *Circuits logiques programmables FPGA*

## I.1 Introduction

FPGA est l'abréviation de Field Programmable Gate Arrays ou "réseaux logiques programmables". Inventés par la société Xilinx en 1985, les FPGA sont des composants logiques de haute densité et reconfigurables qui permettent, après programmation, de réaliser des fonctions logiques, des calculs, et des générations de signaux. Il s'agit d'un circuit intégré qui peut être programmé pour fonctionner selon la conception prévue. Cela signifie qu'il peut fonctionner comme un microprocesseur, ou comme une unité de cryptage, ou une carte graphique, ou même tous ces trois à la fois.

L'avantage de ce genre de circuit est sa grande souplesse qui permet de les réutiliser à volonté dans des algorithmes différents en un temps très court. Les FPGAs peuvent être utilisés pour implémenter n'importe quelle fonction logique que les Circuits intégrés spécifiques ASICs (Application Specific Integrated Circuit) peuvent implémenter. Leur reconfiguration, qui peut être effectuée un nombre arbitraire de fois, représente l'un de leurs avantages majeurs par rapport aux ASICs [I.1], [I.2], [I.3].

Les conceptions fonctionnant sur des FPGA sont généralement créées à l'aide de langages de description de matériel tels que VHDL et Verilog.

Le présent chapitre décrit les FPGAs ainsi que les principaux composants et éléments qui les caractérisent, leurs avantages et différents domaines d'applications. Pour terminer le chapitre, nous décrivons brièvement une rapide présentation de notre carte de développement d'Altera qui contient un circuit FPGA de la famille Cyclone IV.

## I.2 Circuits Logiques Programmables du type FPGA

Les FPGA, sigle anglais qui signifie « Field Programmable Gates Arrays » traduit en français par réseau de portes programmables, sont des circuits intégrés reprogrammables. Ils offrent la possibilité de réaliser des fonctions numériques plus ou moins complexes, tout comme leurs homologues figés : les ASIC [I.4], [I.5], [I.6].

Les FPGAs, sont des composants électroniques programmables de la famille des PLDs (Programmable Logic Device). Un FPGA est un ensemble de blocs logiques élémentaires que l'utilisateur peut interconnecter pour réaliser les fonctions logiques de son choix. La densité des portes est importante et sans cesse en évolution. L'avantage d'un FPGA est leur grande souplesse dans leur technologie permettant une réutilisation à volonté et en un temps très court (quelques millisecondes) dans des algorithmes différents. Le progrès technologique permet de faire des composants toujours plus rapides et à plus haute intégration, autorisant la programmation d'applications importantes [I.7].

Grâce à l'évolution des procédés de fabrication, ces composants peuvent actuellement supporter des applications complexes. Ils sont constitués d'un réseau de blocs logiques, de blocs mémoires, de blocs dédiés et d'entrées/sorties. L'ensemble est relié par un réseau d'interconnexions programmable. Les blocs logiques permettent de réaliser des opérations avec quelques variables à travers une LUT (Look Up Table) [I.8]. Le résultat peut être éventuellement stocké dans un registre, les blocs RAM permettent d'implanter des mémoires adressables et des FIFO (First In, First Out), les blocs dédiés permettent de réaliser facilement de nombreuses opérations de traitement (blocs DSP), de gérer l'horloge, ou des interfaces de communication (Rocket IO, Ethernet, PCI Express). Les nombreux ports permettent également de connecter des périphériques de la plateforme matérielle à base de FPGA.

Les FPGA se programment grâce à leurs LUT et leur réseau d'interconnexion. La programmation se fait avec un langage de programmation hardware tel que le VHDL ou bien le Verilog. L'outil de développement transforme cette description en un fichier de configuration du FPGA en plusieurs étapes : le HDL (Hardware Design Language) doit d'abord être synthétisé (transformé en éléments logiques de base), puis les éléments doivent être placés sur le composant (placement) et enfin interconnectés (routage) [I.9].

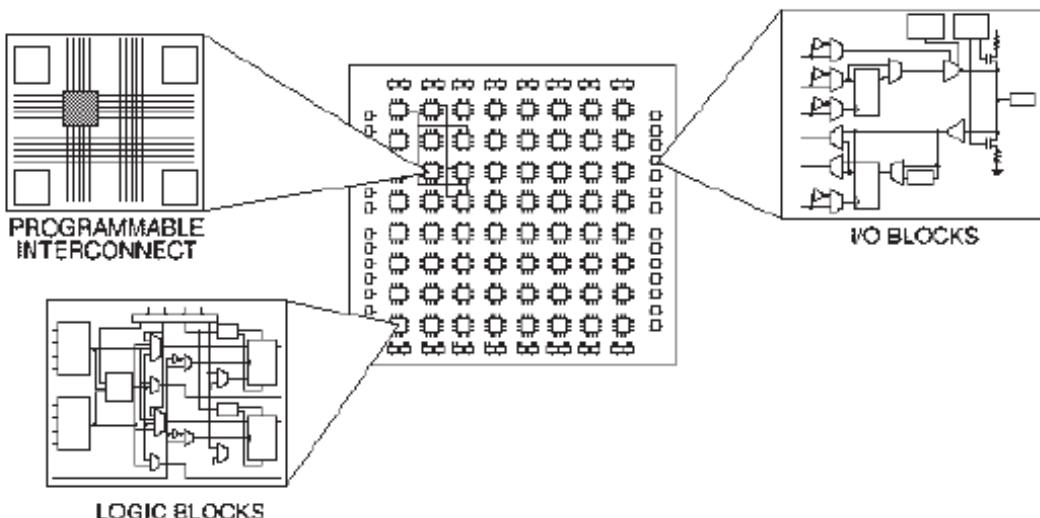

La figure I.1 montre la structure interne d'un FPGA de type matrice symétrique. Il s'agit de l'architecture que l'on retrouve dans les FPGA actuels.

L'utilisateur peut programmer la fonction réalisée par chaque cellule (CLB: Configurable Logic Block). On programme aussi les interconnexions entre les cellules. .

Les FPGA les plus récents sont configurables en une centaine de millisecondes. Les FPGA sont utilisés pour un développement rapide et bon marché des ASIC [I.10].

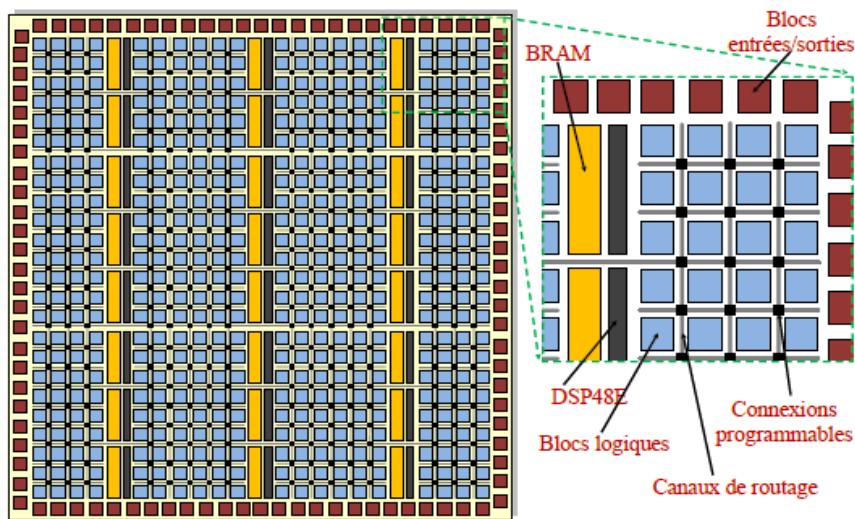

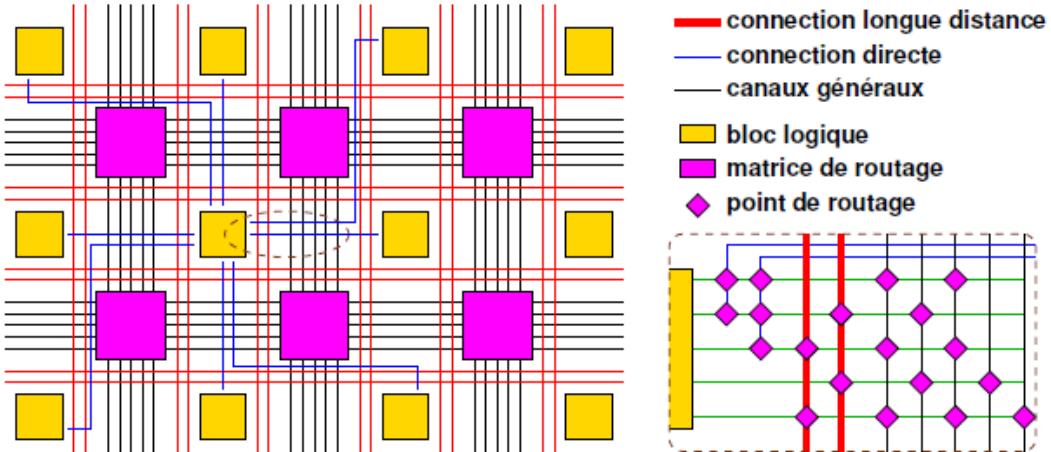

**Figure I.1 :** Architecture conceptuelle d'un FPGA (Architecture, Interconnexions et CLB).

### I.2.1 Architecture [I.10]

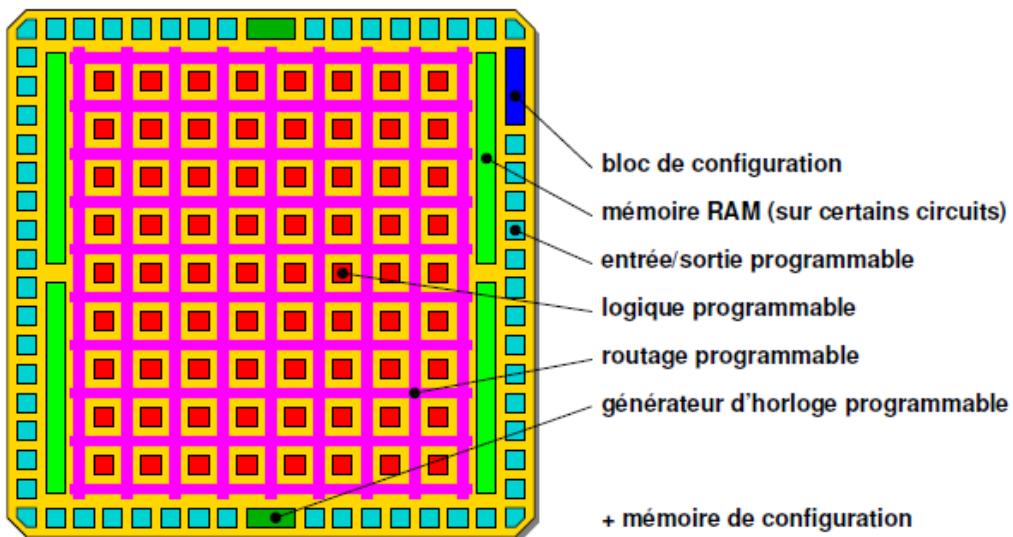

Structurés sous forme de matrices, les FPGA sont composés d'éléments logiques de base, constitués de portes logiques, présentes physiquement sur le circuit. Ces portes sont reliées par un ensemble d'interconnexions modifiables : d'où l'aspect programmable du circuit.

**Figure I.2 : Architecture interne des FPGAs**

**Figure I.3 : Différents secteurs d'un FPGA**

La structure du FPGA présentée figure I.2 est composée :

- ❖ **De cellules d'entrées sorties modifiables** qui servent d'interfaces entre les broches du circuit et le cœur du FPGA pour adapter les signaux suivants :

- Alimentation

- Signaux d'horloge

- Signaux de configuration du FPGA

- Signaux de test

- ❖ De **blocs logiques ou éléments logiques** contenant les fonctions logiques combinatoires et séquentielles.

- La partie combinatoire permet de réaliser des fonctions de complexité moyenne avec des portes classiques ET, OU et NON de deux à une dizaine d'entrées.

- La partie séquentielle comporte une ou deux bascules généralement de type D.

Compte tenu du nombre d'éléments logiques et de leur structure, leur association permet de réaliser tous les types de bascule. L'intérêt est de créer des mémoires élémentaires à un bit.

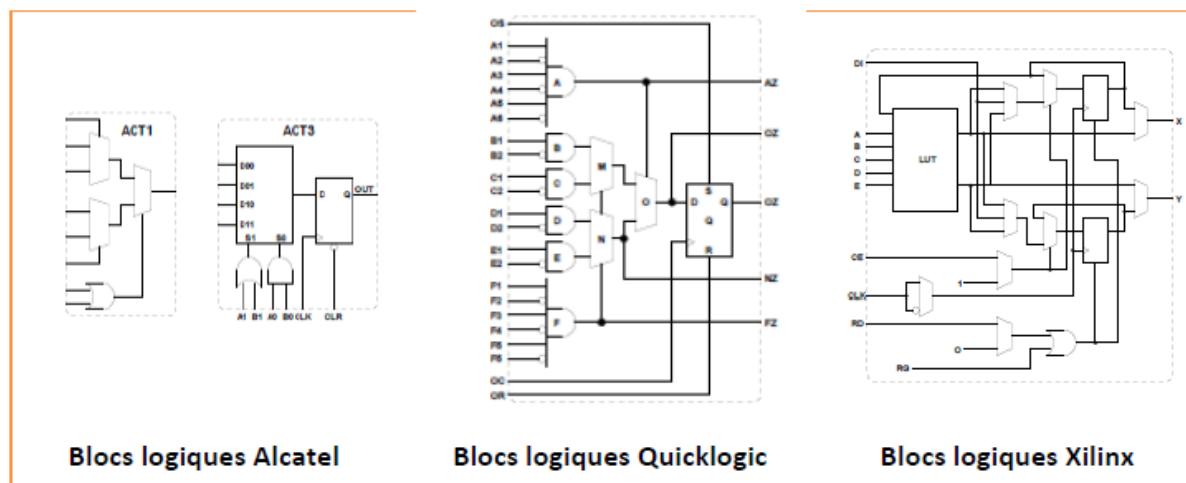

Suivant le fabricant du circuit, ces blocs contiennent un nombre différent de portes logiques et de bascules à l'intérieur d'un bloc comme le montre la figure II.4.

**Figure II.4 :** Exemple de blocs logiques de différents fabricants

Il existe 4 types de blocs logiques :

Les macro-cellules : Ces cellules logique sont appellé aussi par :

- ✓ Soit CLB (configurable logic block), dénomination adoptée par XILINX.

- ✓ Soit LC (cellule logique), le nom choisi par CYPRESS.

- ✓ Soit LE (élément logique), l'appellation d'ALTERA.

- ❖ **De réseaux d'interconnexions** que l'on voit en figure II.5. Ces réseaux relient entre eux les blocs logiques et les blocs d'entrées/sorties. Ces connexions peuvent directement relier :

- **Des éléments internes** dans un bloc grâce à un système de tables logiques appelées LUT. C'est une matrice de connections où les points de routage déterminent le niveau des entrées soit haut soit bas des portes logiques.

- **Des éléments proches** : on parle de liaisons directes entre les blocs.

- **Plusieurs blocs présents sur toute la surface** : on parle de liaisons à distance ou générales.

Certains de ses canaux sont spécifiques aux signaux d'horloges.

**Figure I.5 :** Structure générale du routage

**Remarque :** L'échelle est fausse (blocs logiques < 5% du circuit).

**Un microprocesseur :** La présence d'un processeur est indispensable pour ordonner les commandes reçues par le FPGA. C'est le chef d'orchestre de tout système informatique, où son rôle est de suivre des instructions qui lui ont été préalablement programmées en langage C.

Habituellement, ce processeur se trouve à l'extérieur du FPGA, mais des constructeurs ont intégré ces systèmes directement dans le FPGA. Il s'agit de

processeur « soft-core » (soft pour logiciel et core pour cœur d'exécution) on parle aussi de système sur puce programmable (SOPC) (System On Programmable Chip). Il communique avec le FPGA grâce au langage de description matérielle VHDL. Ce processeur est donc reconfigurable pouvant ainsi d'adapter aux contraintes de chaque utilisation.

## ASICs

Dans la littérature, le terme ASIC (Application Specific Integrated Circuit) est employé pour décrire l'ensemble des circuits spécifiques à une application. Or, dans le langage courant, le terme ASIC est presque toujours utilisé pour décrire les circuits réalisés chez un fondeur. On désigne, par le terme générique PLD (Programmable logic Device), l'ensemble des circuits programmables par l'utilisateur.

### I.2 .2 FPGAs : illustration avec la famille Cyclone IV d'Altera

S'appuyant sur le succès des FPGA Cyclone et pour accroître son leadership sur les interfaces haut débit, Altera Corporation présente sa nouvelle gamme de FPGA Cyclone IV. Afin de répondre à l'augmentation des besoins en bande passante au moindre coût provoquée par la demande en vidéo mobile, en voix, en accès aux données et en images 3D de qualité, la nouvelle gamme de FPGA Cyclone IV ajoute la prise en charge des protocoles série standards et offre le meilleur compromis en coût, puissance et en fonctionnalités logiques, mémoire et DSP [I.11].

**Figure I.6 :** Symbole de Cyclone IV d'Altera.

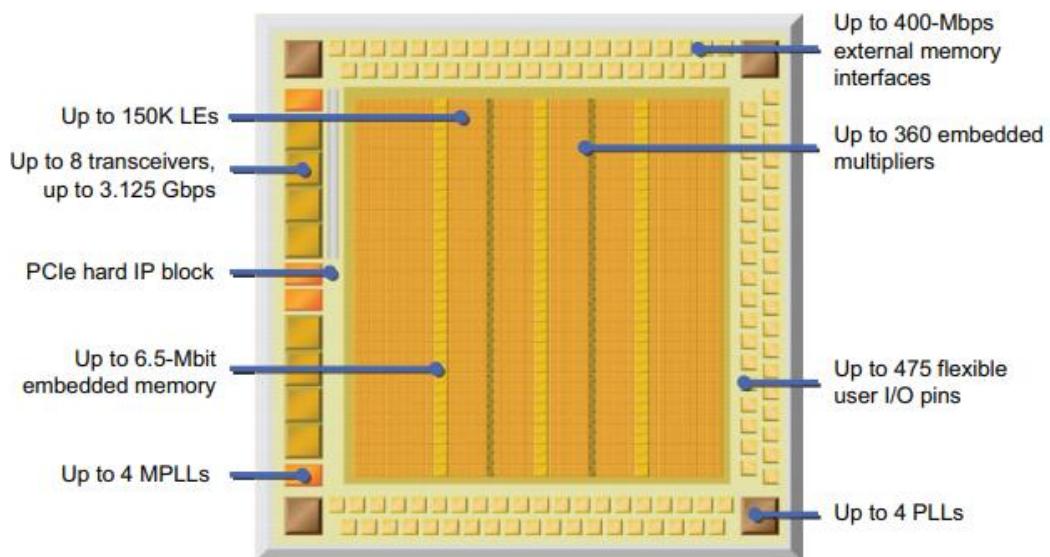

La gamme de FPGA Cyclone IV offre deux variantes. Les circuits Cyclone IV GX possèdent jusqu'à 150K éléments logiques, 6.5Mbits de RAM, 360 multiplicateurs et 8 interfaces haut débit. Avec une basse consommation et un boîtier de 11x11 mm seulement, ces circuits conviennent aux applications à taille réduite et à faible coût des marchés sans fil, filaire, télédiffusion, industriel et grand public. Les circuits Cyclone IV E associent faible coût et hautes fonctionnalités et diminuent d'au moins de 25% la consommation par rapport à la génération précédente de FPGA Cyclone dans les applications basse consommation comme la radio logicielle portable [I.11].

**Figure I.7 :** Caractéristiques architecturales clés du FPGA Cyclone IV [I.12].

L'architecture de Cyclone IV E comprend jusqu'à 115 K éléments logiques disposés verticalement (LE).

### ❖ Elément logique (LE) Cyclone IV

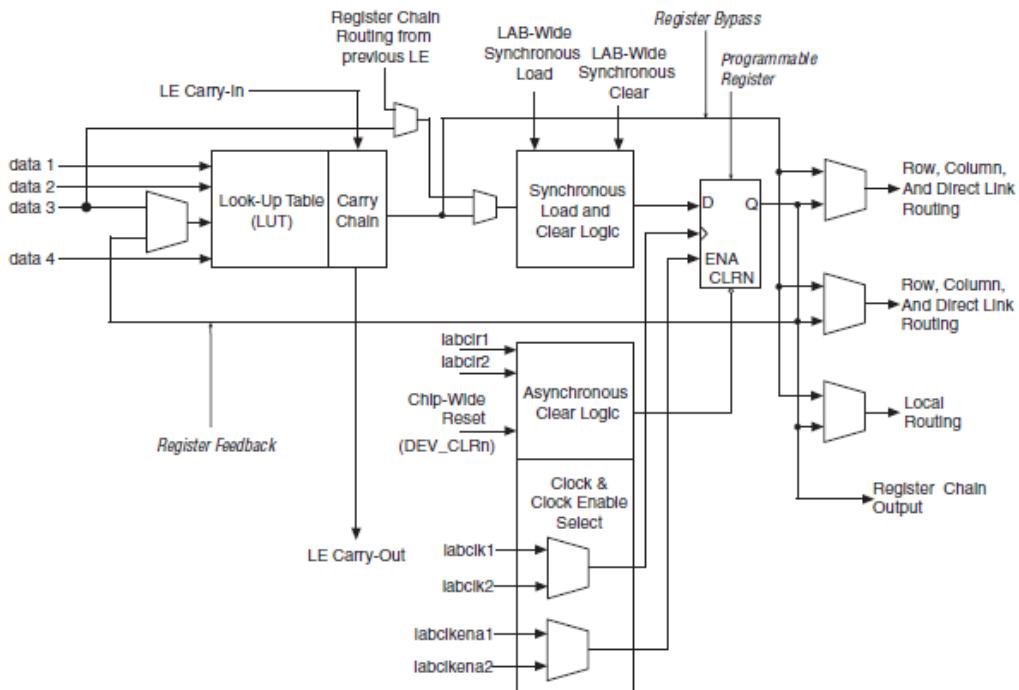

C'est le plus petit élément de logique dans le Cyclone IV. Sa structure apparaît sur la figure ci-dessous :

**Figure I.8 :** Structure d'un Logic Element LE [I.13].

Cette cellule reconfigurable contient divers éléments :

- Une LUT (Look up table) à quatre entrées, permettant le calcul de n'importe quelle fonction de 4 entrées.

- Un registre de sortie programmable

- Une connexion de chaîne de transport

- Une connexion de chaîne de registre

- La possibilité de piloter les interconnexions suivantes :

- ✓ Locale

- ✓ Ligne

- ✓ Colonne

- ✓ Chaîne d'enregistrement

- ✓ Lien direct

- Enregistrez le support d'emballage

- Enregistrez le support de rétroaction

### ❖ Blocs de réseaux logiques (LAB)

Un bloc de réseaux logiques contient :

- 16 Eléments Logiques (LE).

- Un réseau d'interconnexion local pour la communication entre LE du même LAB (voir figure I.9).

- Un accès direct aux éléments adjacents du LAB dans la structure du FPGA (voir figure I.9) tels que :

- ✓ un autre LAB.

- ✓ un bloc mémoire pour les LAB adjacents aux zones mémoires.

- ✓ un signal d'horloge d'une PLL.

- ✓ un multiplexeur.

- ✓ un IOE (Elément d'entrée/sortie).

- ✓ un accès aux réseaux d'interconnexions lignes/colonnes pour atteindre n'importe quel point du composant.

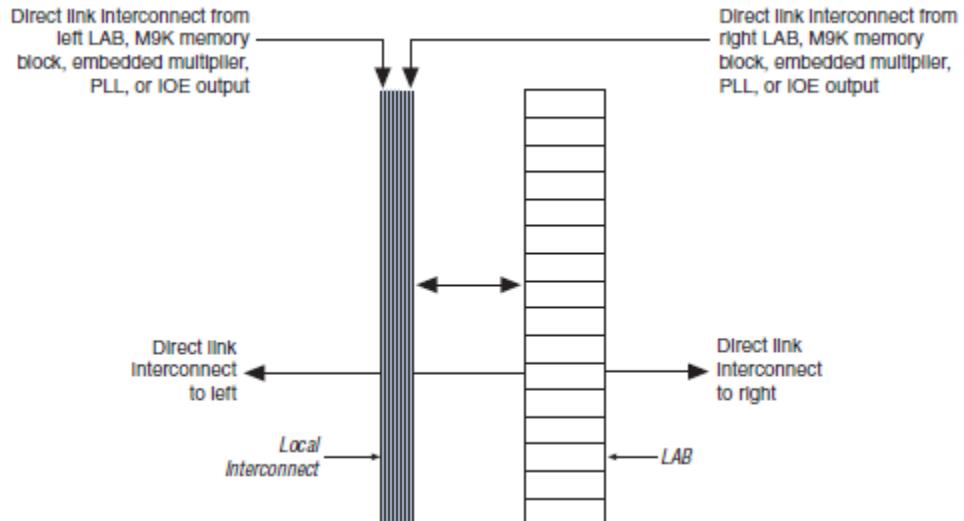

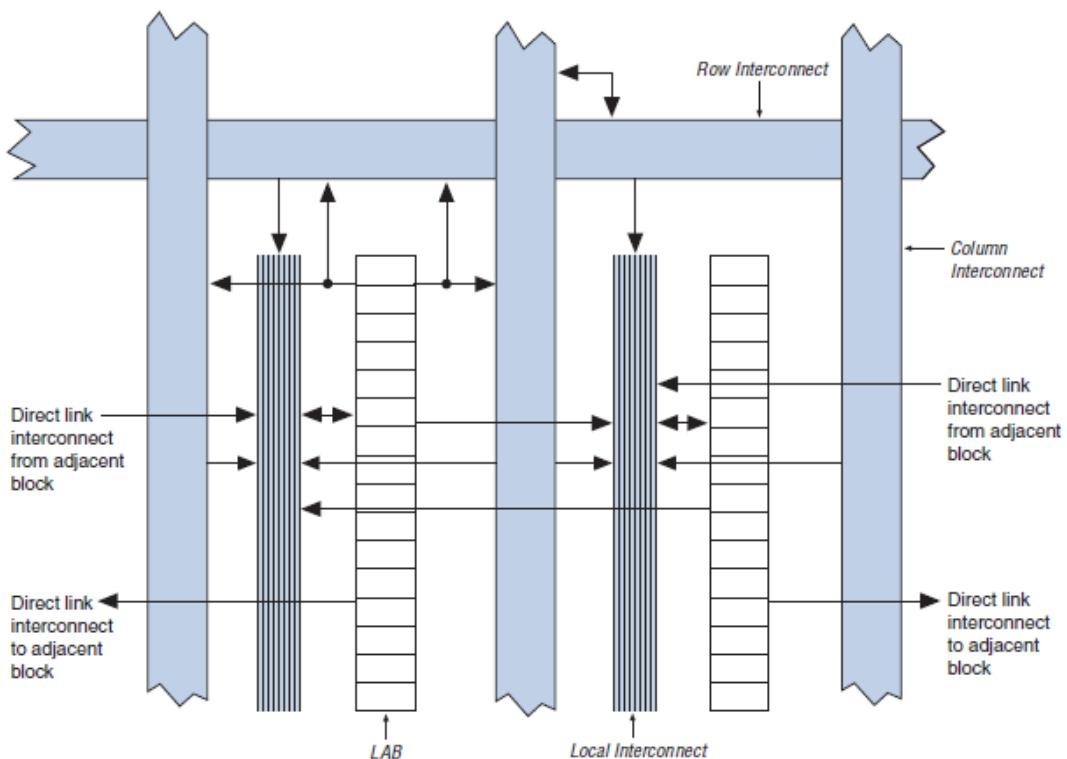

L'interconnexion locale LAB est pilotée par des interconnexions de colonne et de ligne et des sorties LE dans le même LAB. Les LAB voisins, les boucles à verrouillage de phase (PLL), les blocs de RAM M9K et les multiplicateurs intégrés de gauche et de droite peuvent également piloter l'interconnexion locale d'un LAB via la connexion de liaison directe. La fonction de connexion directe minimise l'utilisation d'interconnexions de lignes et de colonnes, offrant des performances et une flexibilité supérieures. Chaque LE peut piloter jusqu'à 48 LE via des interconnexions de liaison locales et directes rapides.

Le compilateur Quartus II place la logique associée dans un LAB ou des LAB adjacents, permettant l'utilisation de connexions de chaînes locales et de registres pour les performances et l'efficacité de la zone.

**Figure I.9 :** Connexions chaînées entre LEs dans un LAB de circuit Cyclone IV [I.13].

**Figure I.10 :** Structure LAB de circuit Cyclone IV [I.13].

### ❖ Bloc d'entrée/sortie (IOE : Input Output Element)

Avec l'accroissement constant du nombre de standards d'entrées/sorties en électronique numérique, la conception d'un FPGA a progressivement nécessité de faire apparaître des blocs dédiés capables d'interfaçages s'adaptant à une grande diversité de situation.

La frange supérieure des composants de la famille Cyclone II dispose donc de nombreux blocs d'entrées/sorties (I/O Banks) répartis à la périphérie du composant.

La famille Cyclone IV peut s'interfacer avec des circuits logiques :

- LVTTL et LVCMS : Interfaçage avec des circuits logiques d'usage général, fonctionnant à des fréquences moins de 100MHz.

- SSTL : Standard mis en place pour la mémoire SDRAM DDR (Double Data Rate).

- HSTL : Signaux des mémoires QDR2 SRAM (Quad Data Rate).

- LVDS (Low Voltage Differential Signaling) : Signaux différentiels (ils garantissent une plus grande immunité au bruit) pour des communications à fort débit (jusqu'à 805Mbps) et faible EMI (émissions électromagnétiques)

- LVPECL (Low Voltage Positive Emitter Coupled Logic) : Signaux différentiels à haute immunité au bruit utilisé en vidéo, télécom, distribution d'horloge.

- PCI et PCI Express Bus locaux des PC utilisés pour la connexion de car et d'extension (Vidéo . . .).

### ❖ Blocs de mémoire dans les appareils Cyclone IV

Les dispositifs Cyclone IV présentent des structures de mémoire intégrées pour répondre aux besoins de mémoire sur puce des conceptions de dispositifs Altera Cyclone IV. La structure de mémoire intégrée se compose de colonnes de blocs de mémoire M9K que vous pouvez configurer pour fournir diverses fonctions de mémoire, telles que la RAM, les registres à décalage, la ROM et les buffers FIFO.

Les blocs M9K prennent en charge les fonctionnalités suivantes :

- 8 192 bits de mémoire par bloc (9 216 bits par bloc, parité comprise)

- Signaux d'activation de lecture (rdn) et d'activation d'écriture (wren) indépendants pour chaque port

- Mode compact dans lequel le bloc de mémoire M9K est divisé en deux RAM à port unique de 4,5 Ko

- Configurations de ports variables

- Prise en charge des modes simple port et double port pour toutes les largeurs de port

- Véritable fonctionnement à deux ports (une lecture et une écriture, deux lectures ou deux écritures)

- L'octet active le masquage d'entrée de données pendant les écritures

- Deux signaux de contrôle d'activation d'horloge pour chaque port (port A et port B)

- Fichier d'initialisation pour pré-charger le contenu de la mémoire en modes RAM et ROM

**PLL:** Les boucles à verrouillage de phase (PLL : Phase Locked Loops) d'un Cyclone II fournit une capacité de synthétiser une horloge principale qui permet la génération de plusieurs horloges internes qui fonctionnent à différentes fréquences issue de l'horloge d'entrée. Chaque PLL peut fournir jusqu'à trois sorties d'horloge pouvant fonctionner à des fréquences différentes. Le PLL est un système qui permet de synchroniser la phase instantanée de deux signaux.

### I.2 .2.1 Puissance de circuit Cyclone IV

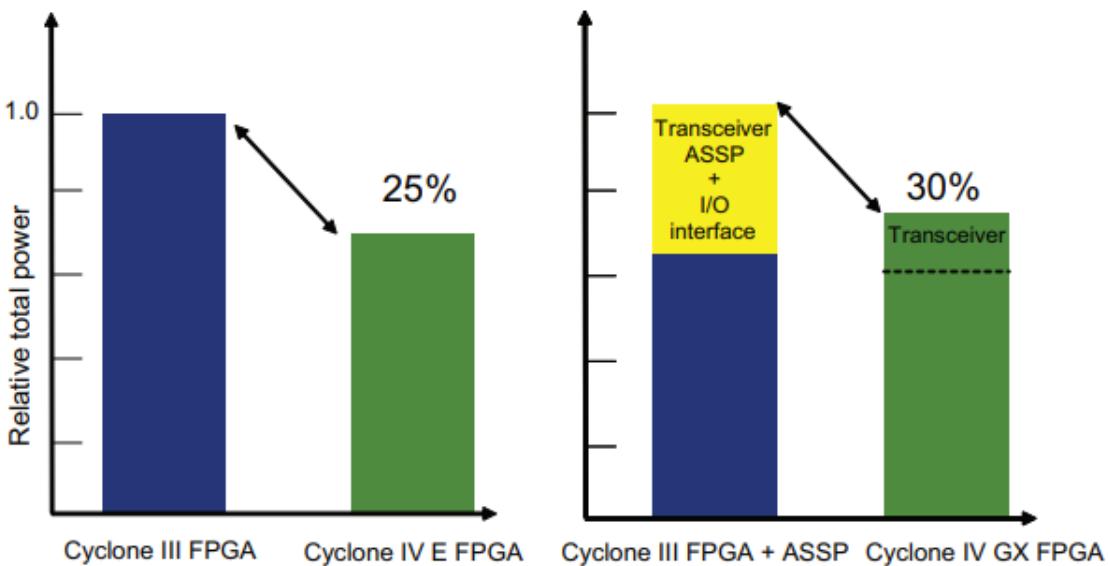

Comme le montre la figure I.11, Altera a travaillé avec son partenaire de fabrication de longue date TSMC pour optimiser le processus de fabrication afin de produire des FPGA avec une puissance statique et dynamique inférieure, jusqu'à 25 % et 30 % de puissance totale en moins respectivement par rapport aux familles Cyclone précédentes [I.14].

**Figure I.11 :** Puissance Cyclone IV E (à gauche) et Cyclone IV GX (à droite) [I.14].

Les FPGA sont synonymes de commercialisation rapide des produits en raccourcissant le calendrier de développement des produits.

Les ingénieurs qui choisissent les FPGA Cyclone IV, avec des performances de cœur jusqu'à 25 % plus rapides (par rapport aux FPGA à faible coût des concurrents), consacreront moins d'itérations de conception à la fermeture temporelle, car une plus grande marge temporelle est disponible. De plus, le logiciel de conception Quartus II d'Altera a des temps de compilation jusqu'à 50 % plus rapides par rapport aux produits logiciels concurrents, ce qui rend les ingénieurs plus productifs, chaque jour au bureau [I.14 ].

### I.2 .2.2 Programmation d'un périphérique de configuration série

Le dispositif Cyclone IV E prend en charge la programmation dans le système d'un dispositif de configuration série à l'aide de l'interface JTAG via la conception du chargeur flash série. Le chargeur flash série est une conception de pont pour l'appareil Cyclone IV E qui utilise son interface JTAG pour accéder au fichier EPCS .jic, puis utilise l'interface AS pour programmer l'appareil EPCS. La figure I.12 illustre la méthode de programmation lors de l'adoption d'une solution de chargeur flash série [I.15].

**Figure I.12 :** Programmation d'un périphérique de configuration série avec une solution de chargeur flash série [I.15].

### I.2 .2.3 Caractéristiques de Cyclone IV EP4CE10 FPGA [I.16]

- ✓ éléments logiques (EL) 10000

- ✓ Boucles de structure et d'E/S à phase asservie (PLL) 2

- ✓ Mémoire embarquée maximale 414 Kb

- ✓ Blocs DSP (Digital Signal Processing) 23

- ✓ Format DSP (Digital Signal Processing) Multiply

- ✓ Contrôleurs de mémoire matériels Non

- ✓ Support mémoire externe (EMIF) DDR, DDR2, SDR

- ✓ Configuration E/S Nombre maximal d'utilisateurs des E/S 179

### I.3 Avantages du FPGA

Ces notions sur le FPGA donnent des indications quant à l'intérêt de son utilisation dans le cadre du projet. Voici les avantages clés qui ont fait que le laboratoire s'est tourné vers cette solution [I.17].

- ✓ **Un circuit reprogrammable** : L'avantage du FPGA est de pouvoir être reprogrammable contrairement aux circuits intégrés de type ASIC. Ce qui rend cette solution modulable et donne la possibilité de modifier le programme générique de base afin de le rendre spécifique au circuit utilisé. Une solution de validation utilisant le FPGA peut alors convenir à beaucoup de projets et donc diffusée à plusieurs équipes.

- ✓ **Un investissement rentable** dans la durée : Cela est dû à sa reprogrammation, ce qui implique une réutilisation à destination d'autres projets, malgré un prix à l'achat supérieur à un circuit ASIC.

- ✓ **Une Reprogrammation quasi-instantanée** du circuit. Une fois le programme validé cela ne prend que quelques minutes à l'implémenter. A titre de comparaison, la fabrication d'un circuit ASIC peut prendre plusieurs semaines.

Cependant, le FPGA n'est pas le seul composant reprogrammable du marché. Le DSP « Digital Signal Processor », processeur de signal numérique, permet également d'émuler un montage numérique. Le DSP est programmable grâce au langage C, le FPGA utilise quant à lui le VHDL. Le format de description machine est généré automatiquement par les logiciels de développement des concepteurs. Il est possible alors de vérifier les circuits sans avoir à les concevoir par nous-mêmes. L'importation de leur fichier dans notre programme est suffisante. Par ailleurs, le FPGA peut disposer d'un DSP sous forme d'IP incluse dans le système du circuit [I.10].

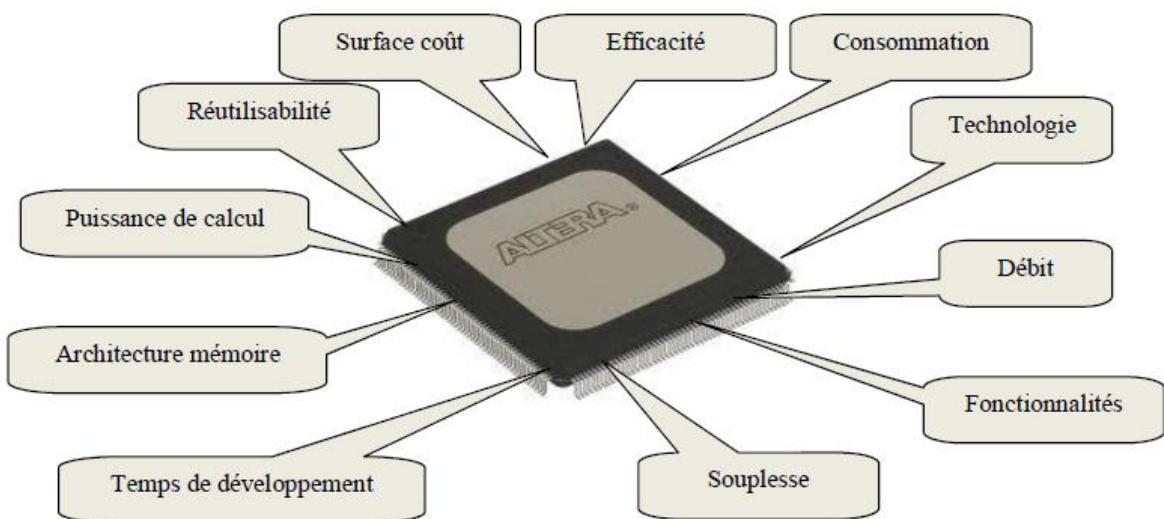

#### I.4 Critères de choix du circuit programmable FPGA [I.18], [I.19]

Les FPGA sont développés récemment grâce aux progrès de la technologie VLSI (Very Large Scale Integration), l'apparition de ce type de circuits est une révolution des systèmes digitaux et ouvrants des perspectives de traitement numérique inaccessibles auparavant. La fin des années 80 a vu l'apparition des premiers circuits FPGA qui sont des circuits intégrés que l'on peut configurer en un temps relativement court pour réaliser n'importe quelle fonction logique « câblée » à bas coût par une programmation de ses cellules logiques et ses interconnexions avec une restriction de ne pas épuiser les ressources du FPGA. Typiquement, un circuit FPGA haute densité peut contenir jusqu'à plusieurs millions d'éléments programmables. Pour réussir une application à base de FPGA et afin d'obtenir un système plus performant, consommant un minimum de puissance, il est nécessaire de respecter un certain nombre de règles comme :

- Bien connaître les caractéristiques du FPGA ciblé pour assurer son adéquation avec les besoins du projet.

- Elaborer une méthodologie de conception.

- Maîtriser les outils d'implémentation et de choisir des outils de synthèse de qualité.

La conception sur les circuits FPGA est un challenge dans lequel l'objectif est de trouver le bon compromis entre densité, flexibilité et performances temporelles.

**Figure I.13:** Critères de choix du circuit logique programmable FPGA.

## I.5 Principaux fondateurs d'FPGA

Les fabricants des FPGA ne cessent pas d'améliorer leurs produits par l'efficacité et la puissance. L'ensemble des firmes (Principaux fondateurs) qui conçoivent ce type de circuits sont : **Altera, Actel, Atmel, Cypress, Lattice, Minc, QuicLogic, Xilinx** et d'autres [I.18].

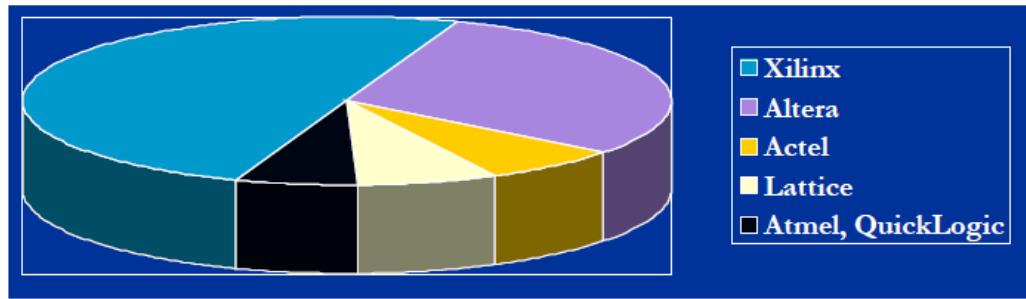

**Figure I.14:** Statistiques du marché occupé par les vendeurs d'FPGA [I.20].

## I.6 Configuration et reconfiguration des FPGA

Un système reconfigurable est un système qui est constitué de composants ou entités à architecture modifiable afin de répondre à un objectif bien déterminé. Ce système reconfigurable dispose d'un mécanisme permettant de choisir une nouvelle configuration et de la mettre en place dans le cadre du processus de reconfiguration. Les circuits FPGA sont un type de ces circuits reconfigurables. Ils sont programmables ou configurables sur les cartes sur quelles ils sont implantés par l'utilisateur. Cette reconfigurabilité est une propriété nécessaire face aux systèmes à charges et contraintes variables [I.18], [I.21].

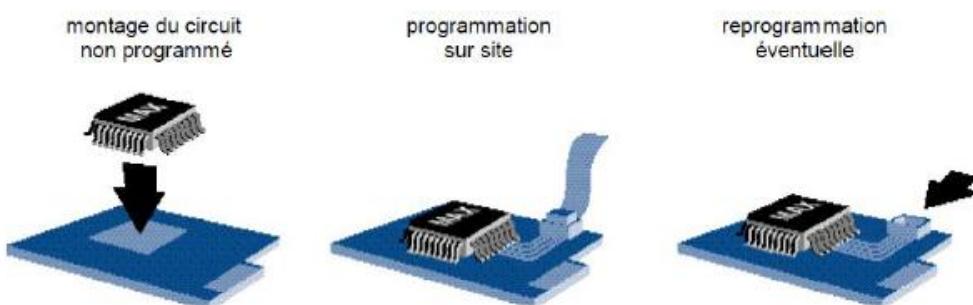

**Figure I.15:** Reprogrammabilité sur site d'un FPGA

## I.7 Méthodologie de conception [I.22]

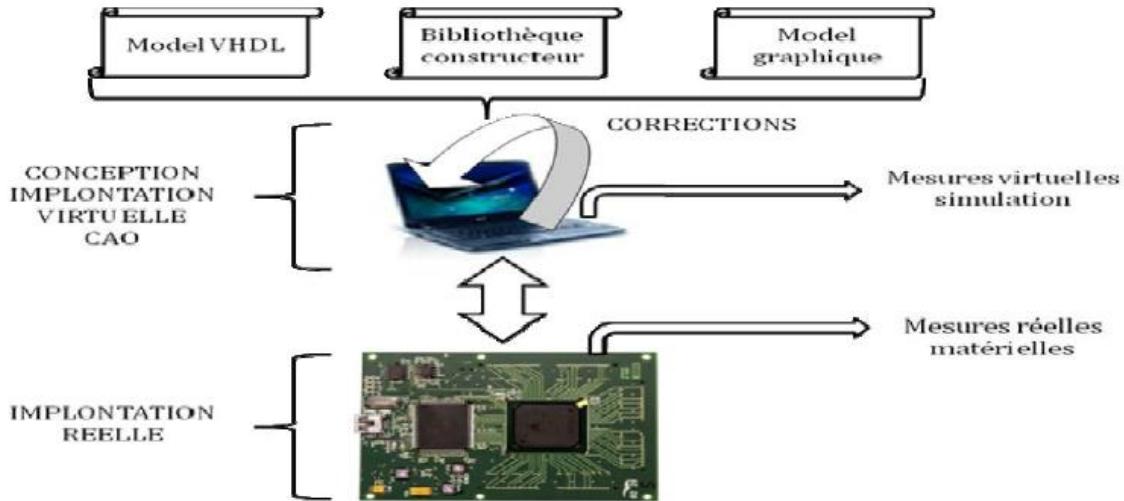

### I.7.1 Outils de CAO (Conception Assistée par Ordinateur) pour la configuration d'un FPGA

Le rôle principal confié aux outils de *CAO* se résume en 4 étapes qui sont : la description, la simulation, la synthèse, le placement et le routage et en dernier la

configuration du FPGA. Un design peut être conçu à l'aide d'un éditeur schématique lors de la conception des circuits simples ou d'un outil de programmation utilisé pour les circuits complexes.

**Figure I.16:** Mode d'exécution matériel des outils de CAO.

### I.7.1.1 Spécification du design

Pour réaliser un circuit, il faut tout d'abord envisager l'architecture globale de ce circuit et spécifier les trois éléments suivants :

- Le nombre de broches d'entrées/sorties et leurs localisations dans le composant FPGA.

- La spécification de la fréquence d'horloge du système.

- La spécification de la mémoire requise pour l'application.

### I.7.1.2 Développement du design

- Spécification de la méthodologie de design (Outil de développement utilisé).

- La saisie du circuit Codage RTL (VHDL, Verilog ...)

- Graphique (Machine à états).

- Saisie HDL (Hardware Description Language).

- La simulation (Prés et Post synthèse).

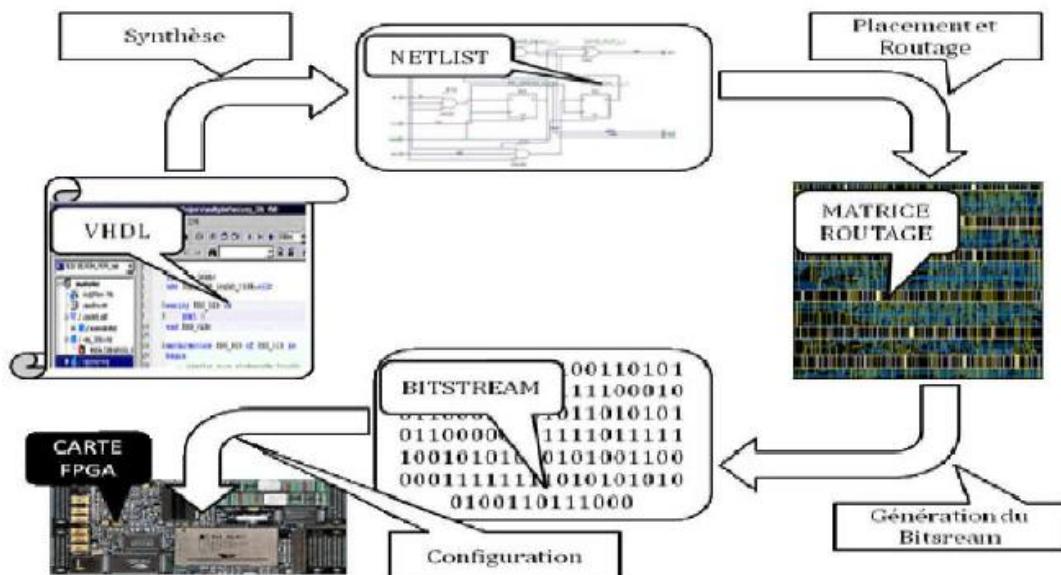

### I.7.1.3 Synthèse

L'outil de synthèse a pour objectifs de minimiser la surface de silicium, le temps de propagation ainsi que la consommation. Cet outil permet de convertir la représentation du design à partir du code HDL fourni pour produire une représentation au niveau de portes logiques. Cette phase s'occupe de déterminer quelles sont les structures susceptibles pour répondre à un cahier des charges étudié et de produire un code sous forme d'un fichier.

### I.7.1.4 Placement et routage

Le placement et le routage sont réalisés en définissant les chemins qui relient l'ensemble des blocs logiques choisies pour notre application à travers un algorithme de routage qui est sensé de faire l'aiguillage des données qu'il reçoit vers leurs destinations par action sur les nœuds de routage.

Plusieurs traitements sont nécessaires pour obtenir un fichier de configuration:

- **Partitionnement:** Les équations logiques spécifiques de notre application sont regroupées en un autre ensemble équivalent d'équations. Chaque équation de ce nouvel ensemble peut être implémentée dans un seul bloc logique du composant FPGA.

- **Placement:** Des blocs logiques sont sélectionnés et affectés au calcul des nœuds du réseau booléen.

- **Routage:** Les ressources d'interconnexion sont affectées à la communication de l'état des nœuds du réseau vers les différents blocs logiques.

- **Génération des données numériques de configuration:** Les informations abstraites de routage, de placement et les équations implantées dans les blocs sont transformées en un ensemble de valeurs binaires, fournies sous forme d'un fichier appelé « bitstream » qui va être envoyé vers le FPGA via une interface de configuration.

### I.7.1.5 Intégration et implémentation

L'implémentation est la réalisation proprement dite qui consiste à mettre en œuvre l'algorithme sur l'architecture du circuit configurable cible, c'est-à-dire à compiler, à charger, puis lancer l'exécution sur un ordinateur ou calculateur. C'est une étape de programmation physique et de tests électriques qui clôturent la réalisation du circuit. La figure suivante résume un peu l'ensemble de ces étapes.

**Figure I.17:** Cycle de programmation d'un FPGA en utilisant les outils de CAO.

### I.8 Principales applications des FPGA [I.23], [I.24]

Ici, nous mettrons en lumière certaines applications clés où la conception avec les FPGA peut être un avantage concurrentiel.

- ✓ Applications Médical

- ✓ Application Militaire

- ✓ Applications Wireline

- ✓ Application Sans fil

- ✓ Véhicules électriques

- ✓ Intelligence artificielle

- ✓ Vision par ordinateur et le prototypage rapide

## I.9 Rapide présentation de la carte de développement d'Altera

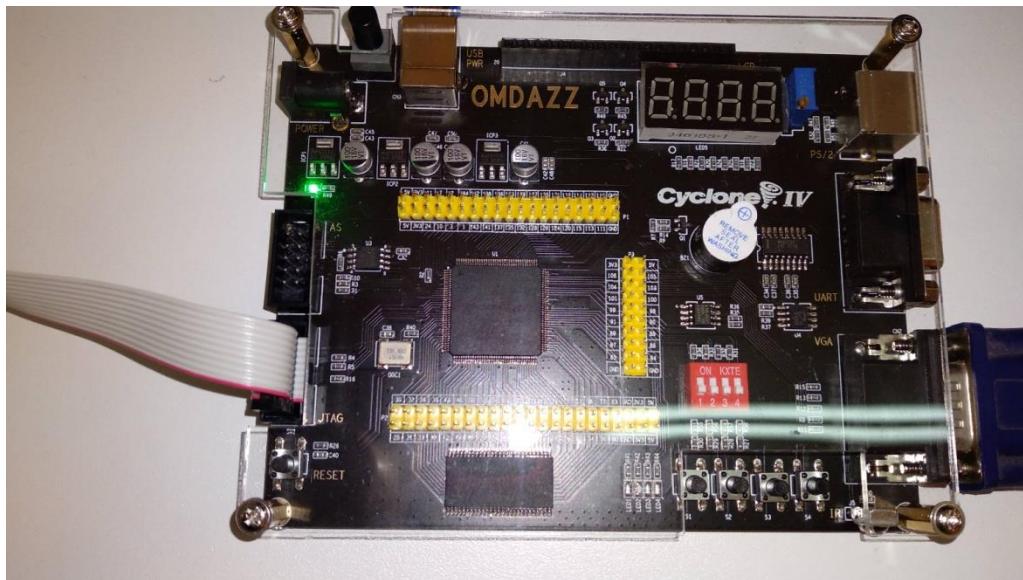

Pour pouvoir être programmé, le FPGA a besoin d'une carte de développement. C'est un environnement de test et de conception. La figure I.18 présente la carte de développement de la série OMDAZZ.

**Figure I.18 :** Carte de développement FPGA Altera Cyclone IV EP4CE10E22C8.

### I.9.1 Caractéristiques de notre composant FPGA EP4CE10E22C8 [I.24]

Le tableau I.1 présente les caractéristiques de notre FPGA.

**Tableau I.1 :** Caractéristiques de FPGA EP4CE10E22C8.

| LE    | I/O | Memory bits | PLL | Global clocks |

|-------|-----|-------------|-----|---------------|

| 10320 | 92  | 423936      | 2   | 10            |

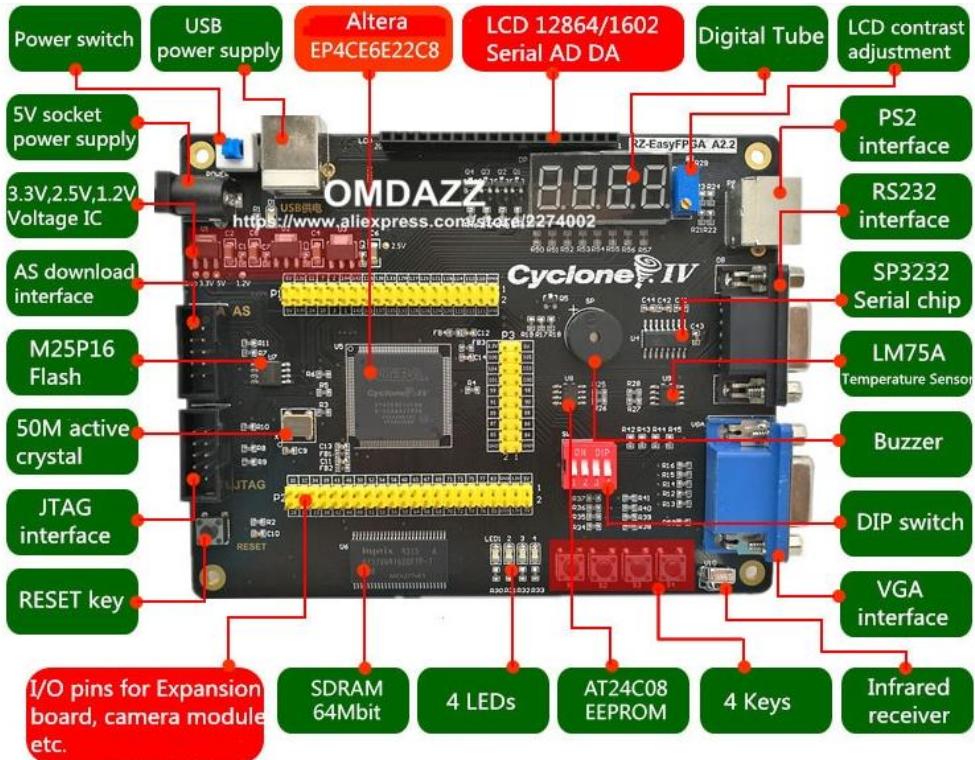

### I.9.2 Différentes parties de la carte OMDAZZ [I.24]

Pour permettre aux utilisateurs de disposer de plates-formes expérimentales excellentes, la série OMDAZZ fournit des plates-formes basées sur ALTERA, le composant supporté est EP4CE10E22C8.

La carte (figure I.19), construite autour d'un FPGA ALTERA Cyclone IV (10320 Logic Elements ou LEs), comporte de la mémoire FLASH, SRAM et

SDRAM, et de nombreux périphériques d'affichage (LEDs, LCD, VGA, TV), sonores et de communication (Ethernet, USB..).

- 1 interrupteur d'alimentation à bouton autobloquant, 1 clé de réinitialisation, 4 clés utilisateur.

- 4 diodes LED.

- tube à 4 chiffres.

- Commutateur DIP à 4 chiffres.

- 1 buzzer.

- interface ps2.

- port série RS232

- 1 prise LCD à 20 broches, prend en charge LCD1602, LCD12864, LCD TFT.

- Résistance réglable avec précision, rétroéclairage LCD réglable.

- Puce de capteur de température LM754A.

- Interface VGA 8 couleurs.

- Série I2C, pour l'expérience du bus IIC

- Module de réception infrarouge.

- Port série RS232.

- Conduit à toutes les broches de la puce principale, avec un espacement de 2.54mm.

**Figure I.19:** Constitution de la carte de développement FPGA Altera Cyclone IV.

## I.10 Conclusion

Dans ce chapitre nous avons vu une présentation des circuits logique programmables FPGAs ainsi que les principaux composants et éléments qui les caractérisent, leurs avantages et différents domaines d'applications, ce qui nous a permis de conclure que la technologie FPGA s'inscrit au sommet de l'évolution des composants logiques et le besoin croissant de composants plus performants, plus économiques et disponibles en grandes quantités avec un faible coût est les grands axes du progrès qui sont disponibles dans les FPGA. Avec ces évolutions c'est tout un nouveau domaine de l'électronique numérique qui s'est ouvert. Aujourd'hui les FPGA sont utilisés dans tous les domaines, des systèmes embarqués aux systèmes de communications, ils sont au cœur d'un important champ de recherche académique et industrielle.

Pour programmer un FPGA nous avons besoin d'un langage de description matériel, dans le chapitre suivant nous allons présenter le langage VHDL, le signal vidéo VGA et son application pour la vision artificielle.

**REFERENCES BIBLIOGRAPHIQUES -CHAPITRE I-**

- [I.1] **AOUICHE Mounir**, « Conception et implémentation d'un Microcontrôleur de 64 bits sur FPGA», Mémoire master en Réseaux et télécommunications Université Mohamed Khider Biskra, 2019.

- [I.2] <http://proxacutor.free.fr/index.htm> ( site consulté le 25/03/2019)

- [I.3] [https://www.cder.dz/vlib/bulletin/pdf/bulletin\\_024\\_05.pdf](https://www.cder.dz/vlib/bulletin/pdf/bulletin_024_05.pdf) Les circuits FPGA : description et applications GUELLAL Amar Attaché de recherche (site consulté le 25/03/2019).

- [I.4] **MARIANI, Johanna**, « Programmation et Utilisation du FPGA pour la validation et la vérification de circuits électroniques », mémoire Présenté en vue d'obtenir Le diplôme d'ingénieur CNAM spécialité : électronique, CENTRE D'ENSEIGNEMENT DE GRENOBLE, 2011.

- [I.5] **TISSERAND Arnaud** : Introduction aux circuits FPGA, Présentation Séminaire MIM, 2003.